# SISTEMAS DIGITAIS

# APONTAMENTOS DAS AULAS TEÓRICAS

**Guilherme Arroz**

Carlos Sêrro

Versão 1.1 3 de Agosto de 2005

Instituto Superior Técnico

Departamento de Engenharia Electrotécnica

e de Computadores

TagusPark

Porto Salvo

#### Historial

| 3 de Agosto de 2005     | v1.1 | Versão corrente.                                                                   |

|-------------------------|------|------------------------------------------------------------------------------------|

| 22 de Fevereiro de 2005 | v1.0 | Foi adicionado o Capítulo 19, e foram feitas correcções no texto da versão 0.2     |

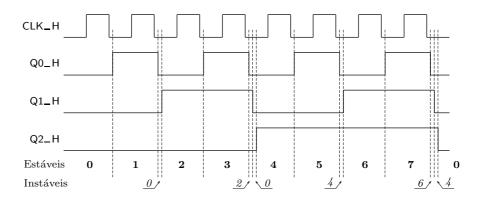

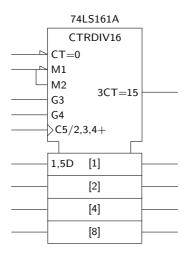

| 6 de Dezembro de 2004   | v0.2 | Foram adicionados os Capítulos 17 e 18, e feitas correcções no texto da versão 0.1 |

| 26 de Outubro de 2004   | v0.1 | Foram adicionados os Capítulos 15 e 16, e feitas correcções no texto da versão 0.0 |

| 14 de Setembro de 2004  | v0.0 | Versão original                                                                    |

#### Referências

Endereço de e-mail: cas@digitais.ist.utl.pt

Página da cadeira de Sistemas Digitais: http://sd.tagus.ist.utl.pt

Versão 1, revisão 1, de 3 de Agosto de 2005

### Prefácio

Este texto foi desenvolvido a partir dos resumos das aulas teóricas da cadeira de Sistemas Digitais das licenciaturas em Engenharia Informática e de Computadores (LEIC), em Engenharia Electrónica (LEE), e em Redes de Comunicação e de Informação (LERCI), leccionados no ano lectivo de 2003/2004 no campus do TagusPark do Instituto Superior Técnico.

Como tal, o presente texto representa uma tentativa de incluir num único local os apontamentos teóricos essenciais à compreensão da matéria de Sistemas Digitais, tal como ela foi ensinada nesse ano lectivo. Por isso, não deve ser entendido como um texto completo, mas sim como uma colecção de resumos teóricos que **não dispensam o estudo mais aprofundado da matéria** por um dos textos referenciados na bibliografia indicada no fim de cada um dos capítulos.

No essencial, o texto segue a matriz das aulas teóricas, tais como elas foram desenvolvidas por um de nós (Guilherme Arroz) e postas à disposição dos alunos nesse ano lectivo. Aqui e ali o texto foi revisto e aumentado, com o objectivo de o tornar mais claro, por vezes mais completo.

#### Organização do texto

O presente texto encontra-se organizado em 3 partes: a primeira trata dos fundamentos teóricos subjacentes a todos os circuitos e sistemas digitais, e cobre os Capítulos 1 a 5; a segunda trata dos circuitos combinatórios, e vai do Capítulo 6 ao Capítulo 11; e a terceira parte lida com os circuitos sequenciais, nos Capítulos 12 a 19.

Em simultâneo desenvolveram-se ainda dois outros textos, pelo que presentemente estão disponíveis:

- o presente documento, com os resumos das aulas teóricas, que designamos por "Sistemas Digitais: Apontamentos das Aulas Teóricas" ou, mais sucintamente, por SD:AAT;

- um manual com a resolução de alguns exercícios, os mais importantes, com o nome "Sistemas Digitais: Exercícios Resolvidos", que designamos abreviadamente por SD:ER; e

- um Glossário, designado simbolicamente por SD:GL.

Em futuras versões prevê-se a inclusão, em SD:AAT, de alguns apêndices com matéria que complementa a que é dada nas aulas teóricas, e que a completa.

Salientam-se, em particular, um apêndice com uma descrição sucinta da notação de dependência usada na Norma IEC 60617-12, e um outro com as regras essenciais que estão na base de um correcto desenho dos diagramas de blocos, dos logigramas e dos esquemas eléctricos. Finalmente prevê-se a inclusão futura de um apêndice que descreve os métodos mais simples de análise que permitem o diagnóstico de falhas nos circuitos digitais.

#### Notas à margem e índice remissivo

Espalhados pelo texto podemos encontrar três tipos de notas à margem:

- chamadas de atenção para partes do texto particularmente importantes, geralmente escritas em itálico; são referenciadas pelo símbolo especial que se mostra nesta margem, à esquerda;

- Este é um comentário obviamente pouco interessante.

- comentários *em itálico* destinados a complementar a matéria; serão incluídos ao longo das sucessivas versões do texto, à medida que a reacção dos alunos a determinados pontos mais obscuros ou difíceis justifique as suas inclusões; e

Os conceitos em **negrito** estão no Glossário — conceitos chave, em **negrito**, que constituem as entradas do Glossário (SD:GL). Nesse sentido, o Glossário é m coadjuvante importante do texto, na medida em que sistematiza os principais conceitos num único documento. Os conceitos são referenciados por entradas à margem, em cor, o que facilita a sua procura após consulta ao Glossário ou ao Índice Remissivo.

No Índice Remissivo encontram-se três tipos de referências: (i) as normais, em tipo direito, para indicar as páginas do texto onde se encontram os conceitos que não precisam de ser salientados de forma especial; (ii) as referências *em itálico*, que identificam as páginas do texto onde existem conceitos chave, em negrito e acentuados à margem; e (iii) as entradas do Glossário ou de outros apêndices, **em negrito**.

#### Agradecimentos

Os autores estão agradecidos aos alunos Paulo Gomes, João Nunes e João Loureiro, que apontaram erros no texto de versões anteriores e que sugeriram, em alguns casos, alterações ao mesmo, com o propósito de o tornar mais claro.

Oeiras, 3 de Agosto de 2005

Guilherme Arroz Carlos Sêrro

# Índice

| Ι | FU  | JNDA   | AMENTOS                                     | 1  |

|---|-----|--------|---------------------------------------------|----|

| 1 | SIS | TEMA   | AS DE NUMERAÇÃO                             | 3  |

|   | 1.1 | Sistem | nas de numeração posicionais                | 3  |

|   |     | 1.1.1  | Representação na base 2                     | 5  |

|   |     | 1.1.2  | Representação na base 16                    | 7  |

|   | 1.2 | Conve  | ersão entre Bases                           | 7  |

|   |     | 1.2.1  | Conversão entre a base 10 e as bases 2 e 16 | 7  |

|   |     | 1.2.2  | Conversão da base 2 para a base 16          | 9  |

|   |     | 1.2.3  | Conversão da base 16 para a base 2          | 9  |

|   |     | 1.2.4  | Truncagens e arredondamentos                | 10 |

|   | 1.3 | Aritm  | ética Binária                               | 12 |

|   |     | 1.3.1  | Adições na base 2 e noutras bases           | 12 |

|   |     | 1.3.2  | Subtracções na base 2 e noutras bases       | 15 |

|   |     | 1.3.3  | Multiplicação na base 2 e noutras bases     | 16 |

|   | 1.4 | Núme   | ros com Sinal                               | 19 |

|   |     | 1.4.1  | Notação de sinal e módulo                   | 19 |

|   |     | 1.4.2  | Notação de complemento para 2               | 19 |

|   | 1.5 | Referê | èncias Bibliográficas                       | 25 |

|   | 1.6 | Exercí | ícios                                       | 25 |

| 2 | CÓ  | DIGO   | ${f S}$                                     | 29 |

|   | 2.1 | Conce  | ito de Código                               | 29 |

|   | 2.2 | Código | os Numéricos                                | 29 |

|   | 2.3 | Código | o Binário Natural (CBN)                     | 31 |

|   | 2.4 |        | o Binário Reflectido (CBR)                  | 31 |

|   |     | 2.4.1  | Construção do CBR a partir do CBN           | 33 |

|   | 2.5 | Código BCD                             | 33 |

|---|-----|----------------------------------------|----|

|   |     | 2.5.1 Representação de números em BCD  | 33 |

|   |     | 2.5.2 Adição em BCD                    | 35 |

|   | 2.6 | Os Códigos m–em–n                      | 36 |

|   | 2.7 | Códigos Alfanuméricos                  | 37 |

|   |     | 2.7.1 O código ASCII                   | 37 |

|   |     | 2.7.2 O código ISO-8859-1              | 38 |

|   | 2.8 | Referências Bibliográficas             | 38 |

|   | 2.9 | Exercícios                             | 39 |

| 3 | ÁLO | GEBRA DE BOOLE BINÁRIA                 | 41 |

|   | 3.1 | Variáveis e Funções Booleanas          | 41 |

|   | 3.2 | Funções com Uma Variável               | 42 |

|   | 3.3 | Funções com Duas Variáveis             | 44 |

|   | 3.4 | Funções com Mais do que Duas Variáveis | 47 |

|   | 3.5 | Axiomas e teoremas                     | 48 |

|   |     | 3.5.1 Axiomas                          | 48 |

|   |     | 3.5.2 Teoremas                         | 48 |

|   | 3.6 | Referências Bibliográficas             | 50 |

|   | 3.7 | Exercícios                             | 50 |

| 4 | REI | PRESENTAÇÃO DAS FUNÇÕES                | 53 |

| 4 |     | Expressões booleanas                   | 53 |

|   | 4.2 | Tabelas de verdade                     | 54 |

|   | 4.3 | O Conjunto {AND, OR, NOT}              | 58 |

|   | 4.4 | Soma de mintermos                      | 58 |

|   | 4.5 | Produto de maxtermos                   | 60 |

|   | 4.6 | Representação por Logigrama            | 62 |

|   | 4.7 | Importância das Funções NAND e NOR     | 64 |

|   | 4.8 | Referências Bibliográficas             | 65 |

|   | 4.9 | Exercícios                             | 65 |

|   | 4.0 | LACTOROUG                              | 00 |

| INDICE      | ••   |

|-------------|------|

| IN(I)II 'H' | 3711 |

| 1181210717  | V11  |

|             |      |

| 5  | MÉ   | MÉTODO DE KARNAUGH 6                       |    |  |

|----|------|--------------------------------------------|----|--|

|    | 5.1  | Simplificação algébrica                    | 69 |  |

|    | 5.2  | Minimização                                | 70 |  |

|    | 5.3  | Adjacências                                | 70 |  |

|    | 5.4  | Quadros de Karnaugh com 4 Variáveis        | 74 |  |

|    | 5.5  | Implicantes e Implicantes Primos           | 76 |  |

|    | 5.6  | Minimização com Indiferenças               | 79 |  |

|    | 5.7  | Quadros de 5 Variáveis                     | 82 |  |

|    | 5.8  | Minimização Usando os Maxtermos            | 84 |  |

|    | 5.9  | O Algoritmo de Karnaugh                    | 87 |  |

|    | 5.10 | Referências Bibliográficas                 | 87 |  |

|    | 5.11 | Exercícios                                 | 88 |  |

|    |      |                                            |    |  |

| II | C    | IRCUITOS COMBINATÓRIOS 9                   | 3  |  |

| 6  | ELE  | EMENTOS TECNOLÓGICOS                       | 95 |  |

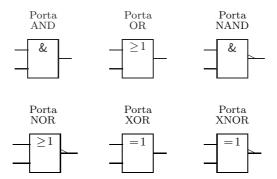

|    | 6.1  | Portas Lógicas                             | 95 |  |

|    | 6.2  | Sinais Binários                            | 96 |  |

|    | 6.3  | Tipos de Circuitos Integrados Digitais     | 97 |  |

|    | 6.4  | A Família TTL                              | 99 |  |

|    |      | 6.4.1 Níveis eléctricos dos circuitos TTL  | 00 |  |

|    |      | 6.4.2 Saídas totem-pole e tri-state        | 01 |  |

|    | 6.5  | A Familia CMOS                             | 03 |  |

|    |      | 6.5.1 Níveis eléctricos dos circuitos CMOS | 03 |  |

|    | 6.6  | Encapsulamento dos Integrados              | 04 |  |

|    | 6.7  | "Fan-out"                                  | 04 |  |

|    | 6.8  | Dissipação de Potência                     | 05 |  |

|    | 6.9  | Tempos de Propagação das Portas            | 05 |  |

|    | 6.10 | Referências Bibliográficas                 | 06 |  |

| 7  | LÓC  | GICA DE POLARIDADE                         | )7 |  |

|    | 7.1  | Lógicas de Polaridade, Positiva e Negativa | 07 |  |

|    |      | 7.1.1 Símbolos dos circuitos digitais      | 07 |  |

|    |      | 7.1.2 Razão da lógica de polaridade        | 09 |  |

|    |      | 7.1.3 Tabelas de verdade físicas e lógicas | 10 |  |

viii ÍNDICE

|    |      | 7.1.4                           | Portas lógicas em lógica de polaridade                                                                                       | 113 |

|----|------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----|

|    |      | 7.1.5                           | Tabelas de verdade genéricas e físicas                                                                                       | 114 |

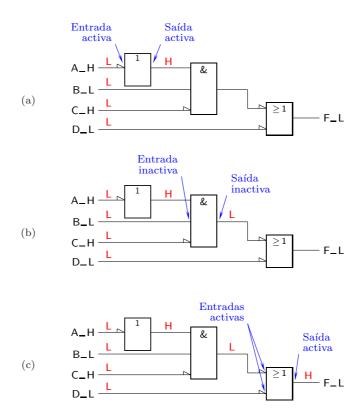

|    |      | 7.1.6                           | Logigramas e esquemas eléctricos em lógica de polaridade                                                                     | 120 |

|    | 7.2  | Conte                           | ído Semântico                                                                                                                | 124 |

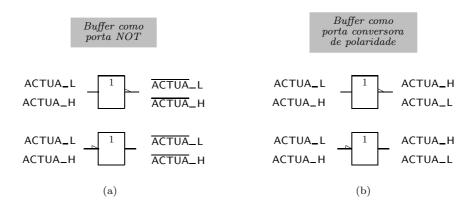

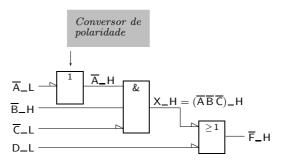

|    |      | 7.2.1                           | Buffers, inversores e conversores de polaridade                                                                              | 127 |

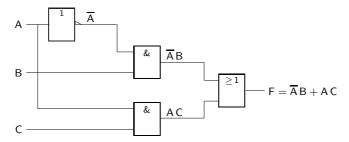

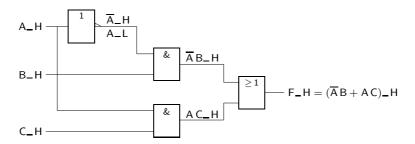

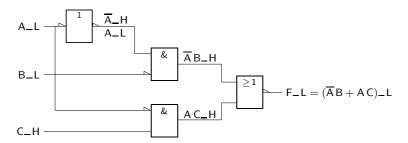

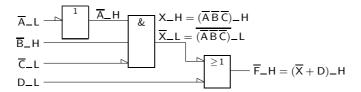

|    | 7.3  | Logigr                          | amas e Expressões Booleanas                                                                                                  | 129 |

|    |      | 7.3.1                           | Geração de logigramas                                                                                                        | 129 |

|    |      | 7.3.2                           | Expressões booleanas a partir de logigramas                                                                                  | 131 |

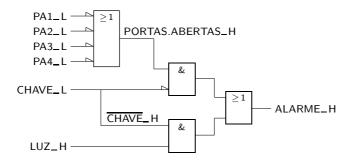

|    | 7.4  | Exemp                           | olo de Utilização                                                                                                            | 136 |

|    | 7.5  | Referê                          | ncias Bibliográficas                                                                                                         | 138 |

|    | 7.6  | Exercí                          | cios                                                                                                                         | 138 |

| 8  | AN   | ÁLISE                           | E SÍNTESE COMBINATÓRIA                                                                                                       | 145 |

|    | 8.1  | Enqua                           | $dramento \dots \dots$ | 145 |

|    | 8.2  | Anális                          | e de Circuitos Combinatórios                                                                                                 | 146 |

|    | 8.3  | Projec                          | to de Circuitos Combinatórios                                                                                                | 148 |

|    | 8.4  | Síntese                         | e de Circuitos Combinatórios                                                                                                 | 151 |

|    | 8.5  | Referê                          | ncias Bibliográficas                                                                                                         | 154 |

|    | 8.6  | Exercí                          | cios                                                                                                                         | 155 |

| 9  | COI  | ODIFICADORES E DESCODIFICADORES |                                                                                                                              | 157 |

|    | 9.1  | Descoo                          | lificadores                                                                                                                  | 157 |

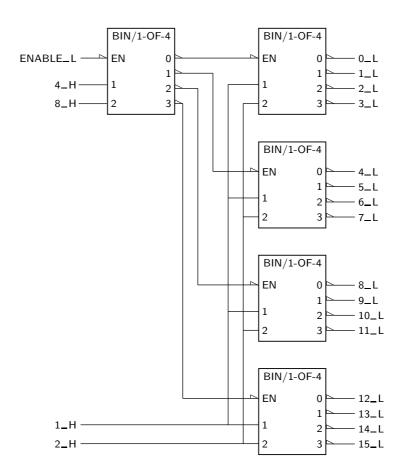

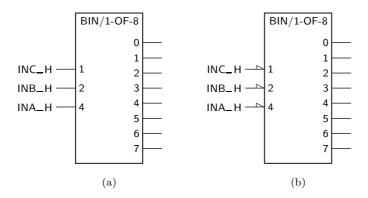

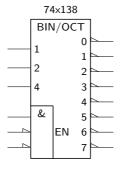

|    |      | 9.1.1                           | Expansão de descodificadores $\dots \dots \dots \dots \dots$                                                                 | 160 |

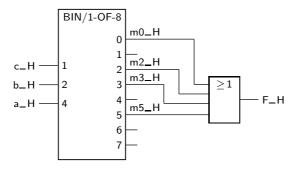

|    |      | 9.1.2                           | Utilização de descodificadores na implementação de funções lógicas                                                           |     |

|    | 9.2  | Codific                         | cadores                                                                                                                      |     |

|    | 9.3  |                                 | ncias Bibliográficas                                                                                                         |     |

|    | 9.4  |                                 | cios                                                                                                                         |     |

| 10 | MU   | LTIPL                           | EXERS E DEMULTIPLEXERS                                                                                                       | 169 |

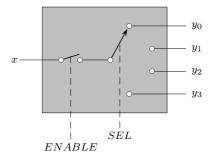

|    | 10.1 | Multip                          | olexers                                                                                                                      | 169 |

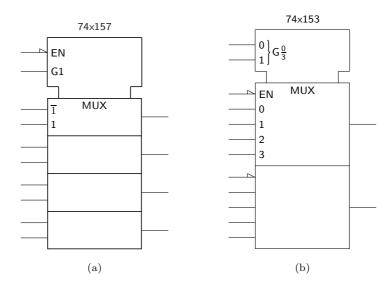

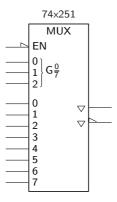

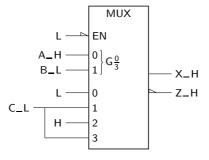

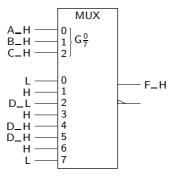

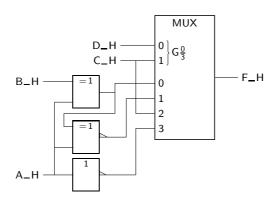

|    |      | 10.1.1                          | Simbolos dos multiplexers                                                                                                    | 172 |

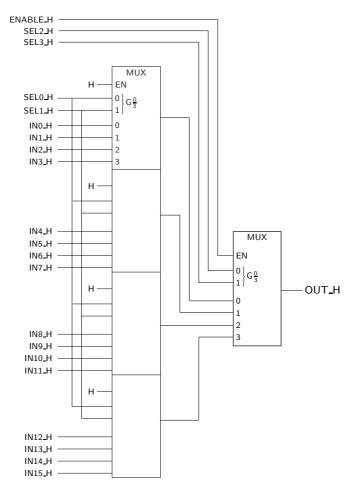

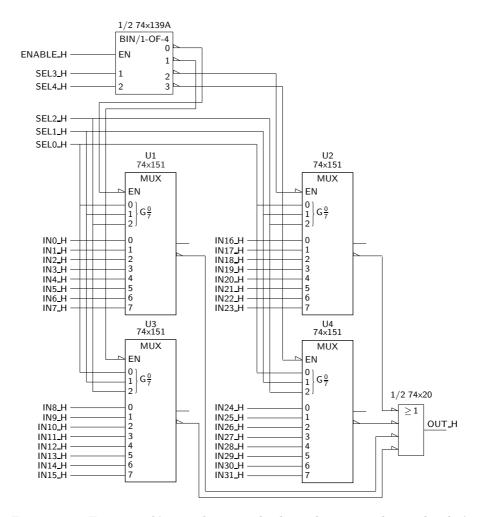

|    |      | 10.1.2                          | Expansão de multiplexers                                                                                                     | 174 |

|    | 10.2 | Demul                           | tiplexers                                                                                                                    | 175 |

|    | 10.3 | Aplica                          | ções dos Multiplexers e dos Demultiplexers                                                                                   | 179 |

|    | 10.4 | Referê                          | ncias Bibliográficas                                                                                                         | 182 |

|    | 10.5 | Exercí                          | cios                                                                                                                         | 182 |

ÍNDICE ix

| 11 CIE | CUITOS ARITMÉTICOS                                                        | 187         |

|--------|---------------------------------------------------------------------------|-------------|

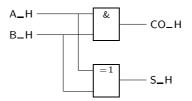

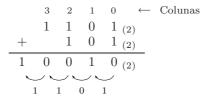

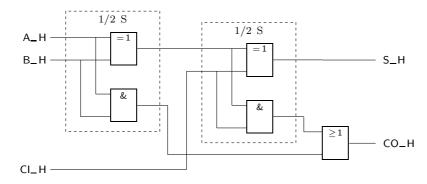

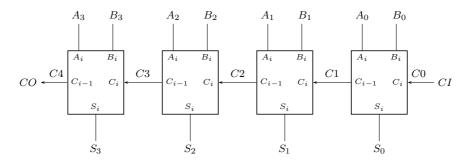

| 11.1   | Somadores Binários                                                        | 187         |

| 11.2   | Subtractores Binários                                                     | 190         |

| 11.3   | Somadores e Subtractores em Complemento para 2                            | 192         |

| 11.4   | Somadores BCD                                                             | 193         |

| 11.5   | Referências Bibliográficas                                                | 195         |

| 11.6   | Exercícios                                                                | 196         |

| III (  | CIRCUITOS SEQUENCIAIS                                                     | L <b>97</b> |

| 12 LAT | TCHES                                                                     | 199         |

| 12.1   | Latches Simples                                                           | 199         |

| 12.2   | Latches Controlados                                                       | 205         |

| 12.3   | Referências Bibliográficas                                                | 210         |

| 12.4   | Exercícios                                                                | 210         |

| 13 FLI | P-FLOPS                                                                   | 217         |

| 13.1   | Flip-flops Master-slave                                                   | 217         |

| 13.2   | Flip-flops Edge-triggered                                                 | 224         |

| 13.3   | Temporizações nos Flip-flops                                              | 227         |

| 13.4   | Referências Bibliográficas                                                | 228         |

| 13.5   | Exercícios                                                                | 228         |

| 14 CO  | NTADORES                                                                  | 233         |

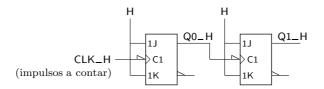

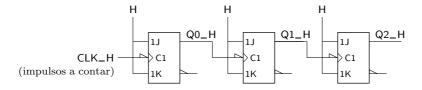

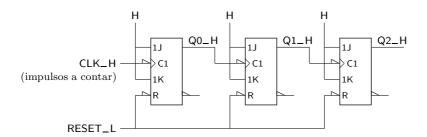

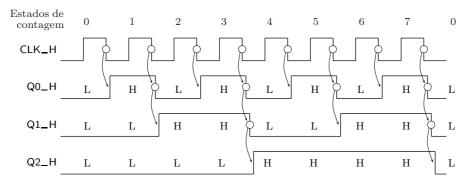

| 14.1   | Contadores Assíncronos                                                    | 233         |

|        | 14.1.1 Flip-flops T                                                       | 235         |

|        | 14.1.2 Diagrama temporal                                                  | 237         |

|        | 14.1.3 Contadores assíncronos com módulos arbitrários $\ \ldots \ \ldots$ | 237         |

|        | 14.1.4 Símbolos dos contadores assíncronos                                | 239         |

| 14.2   | Contadores Síncronos                                                      | 240         |

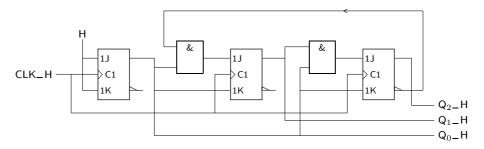

|        | 14.2.1 Concepção heurística de um contador síncrono $\dots \dots$         | 240         |

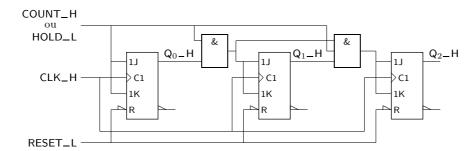

|        | 14.2.2 Contadores síncronos com entrada de Enable $\dots$                 | 243         |

|        | 14.2.3 Concepção de contadores síncronos de módulo qualquer $$ .          | 243         |

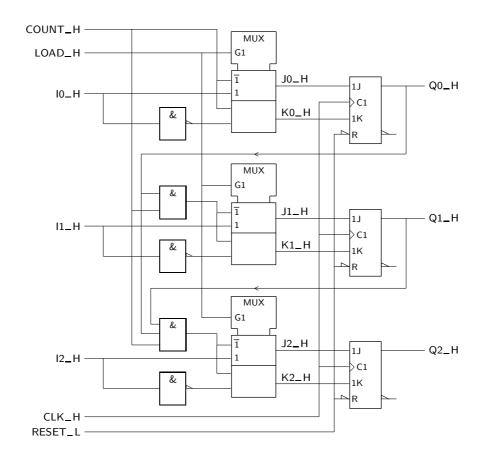

|        | 14.2.4 Contadores síncronos com vários modos de funcionamento             | 246         |

|        | 14.2.5 Contadores síncronos com carregamento em paralelo                  | 247         |

| x | ÍNDICE |

|---|--------|

|    | 14.3 | Símbolos dos Contadores                                                                                        |

|----|------|----------------------------------------------------------------------------------------------------------------|

|    | 14.4 | Estados Instáveis                                                                                              |

|    | 14.5 | Interligação de Contadores                                                                                     |

|    | 14.6 | Carregamento em Paralelo                                                                                       |

|    | 14.7 | Referências Bibliográficas                                                                                     |

|    | 14.8 | Exercícios                                                                                                     |

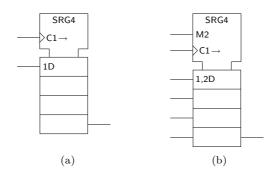

| 15 | REC  | GISTOS 263                                                                                                     |

|    | 15.1 | Conceito de Registo                                                                                            |

|    | 15.2 | Registos Simples                                                                                               |

|    | 15.3 | Registos com Enable                                                                                            |

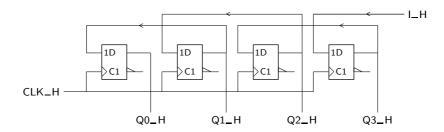

|    | 15.4 | Registos de Deslocamento                                                                                       |

|    | 15.5 | Registos Multimodo                                                                                             |

|    | 15.6 | Transferências entre Registos                                                                                  |

|    |      | 15.6.1 Interligação de registos                                                                                |

|    |      | 15.6.2~ Interligação entre registos utilizando multiplexers 270                                                |

|    |      | 15.6.3 Buffers tri-state                                                                                       |

|    |      | 15.6.4Interligação entre registos utilizando barramentos tri-state $276$                                       |

|    | 15.7 | Referências Bibliográficas                                                                                     |

|    | 15.8 | Exercícios                                                                                                     |

| 16 | CIR  | CUITOS SEQUENCIAIS SÍNCRONOS 281                                                                               |

|    | 16.1 | Circuitos Síncronos e Assíncronos                                                                              |

|    | 16.2 | Modelo de um Circuito Sequencial Síncrono                                                                      |

|    | 16.3 | Análise dos Circuitos Sequenciais Síncronos $\ \ldots \ \ldots \ \ldots \ 283$                                 |

|    | 16.4 | Modelos de Mealy e de Moore                                                                                    |

|    | 16.5 | Síntese de Circuitos Sequenciais Síncronos                                                                     |

|    | 16.6 | Exemplo de Concepção de Diagramas de Estados 289                                                               |

|    |      | 16.6.1Concepção de diagramas de estados: modelo de Moore $290$                                                 |

|    |      | 16.6.2 Concepção de diagramas de estados: modelo de Mealy $293$                                                |

|    | 16.7 | Síntese Clássica                                                                                               |

|    |      | 10 F 1 C( ) C( ) F1                                                                                            |

|    |      | 16.7.1 Síntese Clássica com Flip-flops D 296                                                                   |

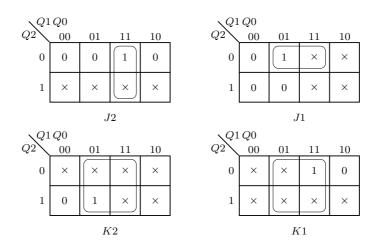

|    |      | 16.7.1 Sintese Clássica com Flip-flops D       296         16.7.2 Síntese Clássica com Flip-flops JK       300 |

|    | 16.8 |                                                                                                                |

|    |      | 16.7.2 Síntese Clássica com Flip-flops JK                                                                      |

|    | 16.9 | 16.7.2 Síntese Clássica com Flip-flops JK                                                                      |

ÍNDICE xi

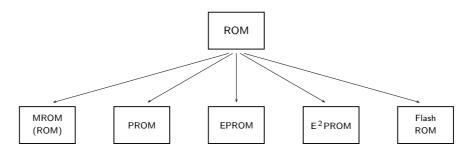

| 17 | MEI  | MÓRIAS                                                                  | <b>32</b> 9 |

|----|------|-------------------------------------------------------------------------|-------------|

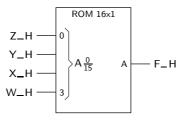

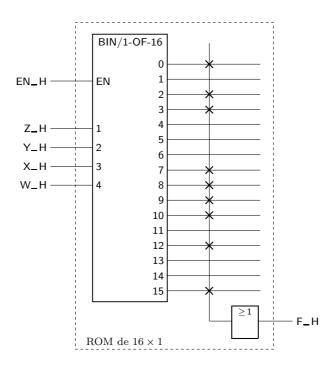

|    | 17.1 | "Read Only Memories" (ROMs)                                             | 330         |

|    |      | 17.1.1 Tipos de ROMs                                                    | 330         |

|    |      | 17.1.2 Utilização das ROMs                                              | 331         |

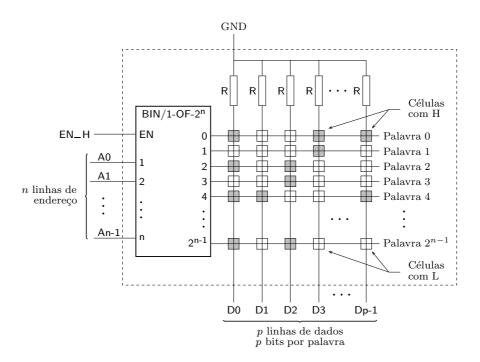

|    |      | 17.1.3 Estrutura de uma ROM                                             | 331         |

|    |      | 17.1.4 Funcionamento de uma MROM                                        | 332         |

|    |      | 17.1.5 Descodificação coincidente                                       | 334         |

|    |      | 17.1.6 Símbolos das ROMs                                                | 334         |

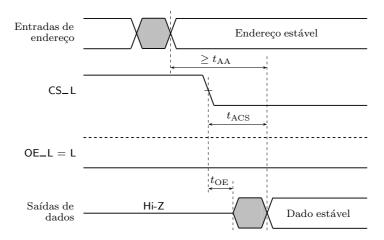

|    |      | 17.1.7 Temporizações na leitura de uma ROM $\ \ldots \ \ldots \ \ldots$ | 336         |

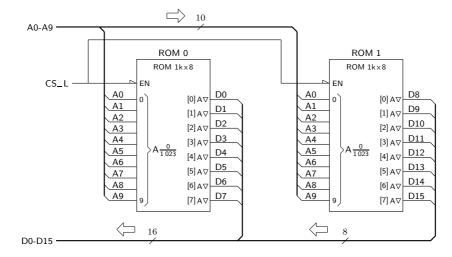

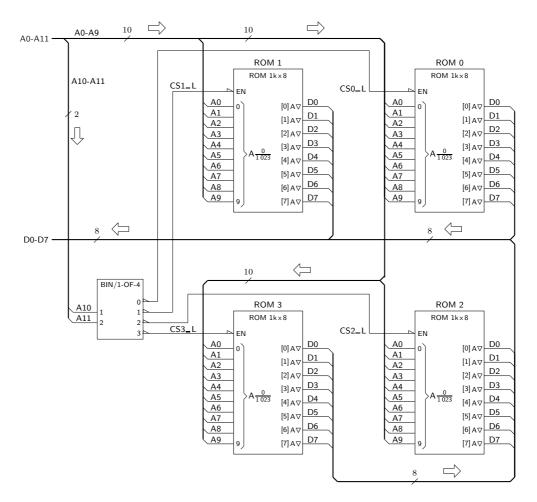

|    |      | 17.1.8 Expansão de ROMs                                                 | 339         |

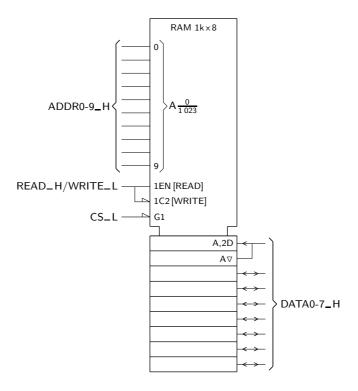

|    | 17.2 | "Random Access Memories" (RAMs)                                         | 341         |

|    |      | 17.2.1 Tipos de RAMs                                                    | 341         |

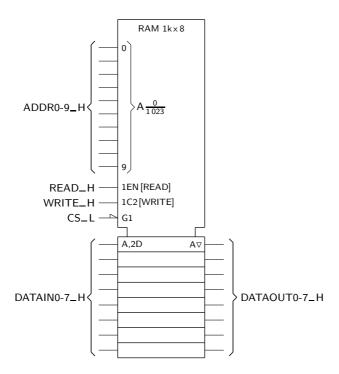

|    |      | 17.2.2 Símbolos das RAMs                                                | 342         |

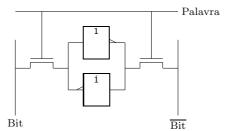

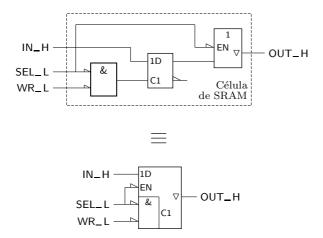

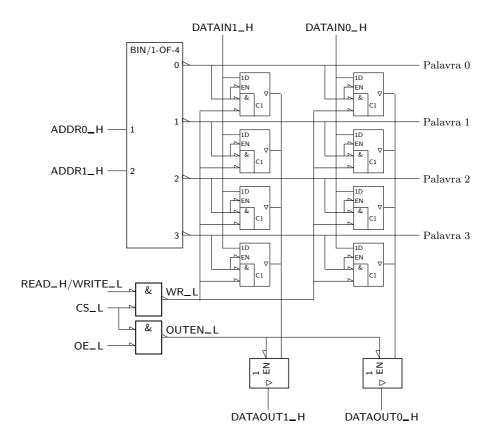

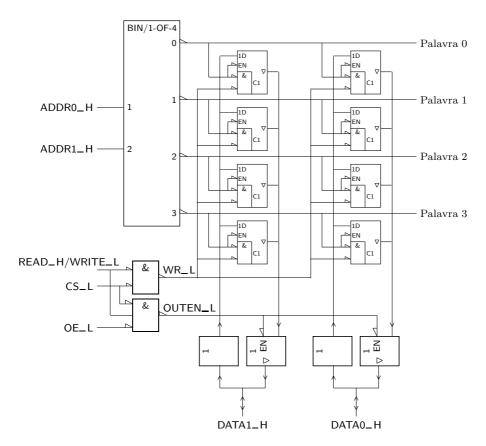

|    |      | 17.2.3 Estrutura de uma RAM estática (SRAM)                             | 344         |

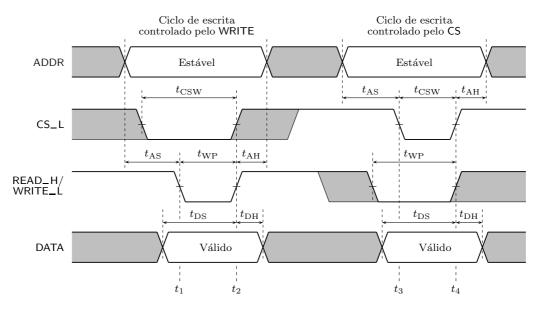

|    |      | 17.2.4 Ciclos de leitura e de escrita numa SRAM                         | 348         |

|    |      | 17.2.5 Expansão de RAMs                                                 | 350         |

| 18 | LÓC  | GICA PROGRAMÁVEL                                                        | 351         |

|    | 18.1 | "Read Only Memories" (ROMs)                                             | 351         |

|    | 18.2 | "Programmable Logic Arrays" (PLAs)                                      | 353         |

|    | 18.3 | "Programmable Array Logic" (PALs)                                       | 358         |

| 19 | MÁ   | QUINAS DE ESTADOS                                                       | 363         |

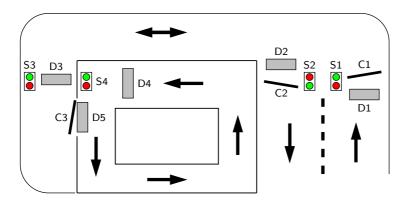

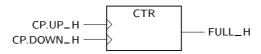

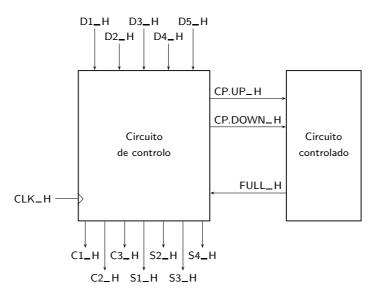

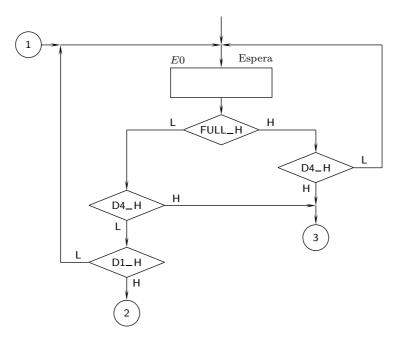

|    | 19.1 | Circuito Controlado e Circuito de Controlo $\ \ldots \ \ldots \ \ldots$ | 363         |

|    | 19.2 | Máquinas de Estados e Fluxogramas                                       | 366         |

|    | 19.3 | Implementação com ROMs                                                  | 367         |

|    |      | 19.3.1 Estrutura básica de controlo por ROM                             | 369         |

|    |      | 19.3.2 Controlo por ROM com endereçamento explícito                     | 373         |

|    |      | 19.3.3 Controlo por ROM com endereçamento implícito                     | 382         |

|    | 10.4 | Erronaígios                                                             | 200         |

xii ÍNDICE

# $\begin{array}{c} \text{Parte I} \\ \\ \textbf{FUNDAMENTOS} \end{array}$

## Capítulo 1

## Sistemas de Numeração

#### 1.1 Sistemas de numeração posicionais

Estamos tão habituados a contar e a executar as operações básicas (adição, subtracção, multiplicação e divisão) usando um sistema decimal, com base b=10, que nem paramos para pensar por um momento nos algoritmos que estão na base dessas operações.

A utilização dessa base era inevitável, já que a humanidade se habituou, desde muito cedo, a contar pelos dedos das mãos. Ocasionalmente usa outros sistemas de numeração. Por exemplo, usa o sistema sexagesimal, com base b=60, para contar as unidades horárias de "minutos" e "segundos", ou o sistema duodecimal com base b=12, ou o sistema de base b=24, para identificar as "horas" do dia.

Todos estes sistemas são **posicionais** ou **ponderados**, na medida em que cada número é formado por uma sequência de **dígitos** ou **algarismos**, em que cada dígito possui um **peso** característico da posição que ocupa na sequência.

Nada nos impede, contudo, de usar sistemas com bases não naturais, por exemplo com bases inteiras negativas, bases racionais e irracionais, reais, ou até bases complexas. E usamos ainda **sistemas não posicionais**, como é o caso do sistema de numeração romano, em que não há pesos associados aos dígitos.

Neste curso vamos estar interessados apenas nos sistemas posicionais (que designamos, mais simplesmente, por **sistemas de numeração**) de base b e, em particular, nos sistemas de numeração binário (com b=2) e hexadecimal (com b=16). Ocasionalmente, refererir-nos-emos a outros sistemas de numeração, com uma base natural arbitrária.

Por outro lado, começaremos por estudar os **números sem sinal**, deixando para a Secção 1.4 o estudo dos números com sinal.

Para que cada quantidade numérica seja expressa por uma e só uma sequência de dígitos, um sistema de numeração de base b arbitrária possui b dígitos, sendo que cada um deles deve exprimir, por si só, um número diferente, menor do que b. Assim, um dígito exprimirá a ausência de qualquer quantidade, usando-se, nesse caso, o símbolo 0 para o representar. Outro dígito expressará a quantidade

Sistema decimal Base 10

Sistema sexagesimal Base 60

Sistema duodecimal Base 12

Sistemas posicionais ou ponderados Dígito ou algarismo

Peso

Sistemas não posicionais

Sistema de numeração de base b

Números sem sinal

unitária, e o símbolo 1 representará esse dígito. Os restantes dígitos exprimirão quantidades de duas, três, quatro, ..., (b-1) unidades.

Um número sem sinal escrito num sistema de numeração de base b, que designaremos por  $N_{(b)}$ , vem representado por uma sequência infinita de dígitos,

$$N_{(b)} <> \cdots d_2 d_1 d_0, d_{-1} d_{-2} \cdots,$$

em que o símbolo <> é utilizado indistintamente para significar que  $N_{(b)}$  "é representado pela sequência", ou que "a sequência representa"  $N_{(b)}$ . Nesta sequência, cada dígito  $d_i$  é ponderado por um peso  $b^i$  associado à sua posição. Se agora efectuarmos a soma polinomial

$$N_{(10)} = \sum_{-\infty}^{+\infty} d_i b^i = \dots + d_2 b^2 + d_1 b^1 + d_0 b^0 + d_{-1} b^{-1} + \dots$$

Equivalente decimal

na base 10, obtemos o equivalente decimal  $N_{(10)}$  de  $N_{(b)}$ .

A igualdade anterior sugere que um número sem sinal deverá ser representado por uma sequência infinita de dígitos. Tal sequência é, naturalmente, impossível de escrever ou de utilizar. Nessas condições, torna-se finita a sequência procedendo às seguintes operações: (i) truncamento dos dígitos não significativos à esquerda da representação, se existirem; (ii) truncamento dos dígitos à direita da representação ou, quando tal não for possível, arredondamento do dígito de menor peso.

Obtemos, nessas condições, uma sequência finita,

$$N'_{(b)} \iff d_{q-1} d_{q-2} \dots d_1 d_0, d_{-1} \dots d_{-p},$$

com precisão eventualmente reduzida em relação à de  $N_{(b)}$ , sequência essa com q dígitos para a esquerda e p dígitos para a direita da vírgula (eventualmente, p pode ser nulo). O equivalente decimal de  $N'_{(b)}$  vem, então, dado pela soma

$$N'_{(10)} \simeq \sum_{i=-p}^{q-1} d_i b^i = d_{q-1} b^{q-1} + \dots + d_0 b^0 + d_{-1} b^{-1} + \dots + d_{-p} b^{-p}$$

.

Um exemplo ajuda a clarificar estas questões. O número  $460,13_{(7)}$  tem por equivalente decimal o número

$$4 \times 7^{2} + 6 \times 7^{1} + 1 \times 7^{-1} + 3 \times 7^{-2} =$$

$$= 4 \times 49 + 6 \times 7 + 1 \times \frac{1}{7} + 3 \times \frac{1}{49}$$

$$= 196 + 42 + 0, 142857 \dots + 0, 061224 \dots$$

$$= 238, 204081 \dots$$

Notemos que este resultado possui uma parte fraccionária infinita. Se a quisermos tornar finita — o que podemos ou não querer fazer, consoante o problema que tivermos em mãos — precisamos de a truncar ou de a arredondar.

Escrevemos, então, por exemplo, que

$$460, 13_{(7)} \simeq 238, 20408_{(10)}$$

se quisermos obter uma precisão de 5 casas decimais fraccionárias (neste caso truncámos a parte fraccionária) , ou

$$460, 13_{(7)} \simeq 238, 2041_{(10)}$$

se apenas precisarmos de 4 casas decimais (neste caso arredondámo-la).

Mais à frente estudaremos a questão da precisão a dar a um número fraccionário, numa base arbitrária, que é como quem diz, a questão da truncagem ou do arredondamento correcto da parte fraccionária.

Uma questão final sobre a designação a dar a um número escrito numa base arbitrária. Estamos habituados a dizer que o número "trinta e sete vírgula cinco" se representa por 37, 5. Mas, naturalmente, tal só é possível num sistema de base 10, em que "trinta" tem o significado de  $3\times 10$ . Ou seja, a frase "trinta e sete vírgula cinco" representa apenas o número  $37,5_{(10)}$  e não possui qualquer espécie de significado em qualquer outro sistema de numeração.

E se quisermos identificar verbalmente o número  $37, 5_{(8)}$ ? Ou o número  $37, 5_{(9)}$ ? Ou ainda o número  $37, 5_{(b)}$ , com  $b \ge 11$ ?

Naturalmente, já não podemos verbalizar esses números da mesma forma. A maneira correcta de o fazer consiste em escrever que o número 37,  $5_{(b)}$  se designa por "três sete vírgula cinco na base b". E isto porque o "três" na base b=10 é ainda o "três" numa base em que  $b\neq 10$  e  $b\geq 4$ , outro tanto acontecendo com os outros dois dígitos.

Pela mesma ordem de razões, dizemos que um número decimal tem "dízima" ou "parte decimal", mas que um número numa base arbitrária  $b \neq 10$  tem "parte fraccionária".

O maior dos dígitos no número  $37,5_{(b)}$  é o 7. Logo, b tem que ser, pelo menos, igual a 8.

#### 1.1.1 Representação na base 2

No sistema binário ou sistema de base b=2 usam-se apenas os dígitos 0 e 1, que também se designam por bits. Assim sendo, um número binário legítimo é, por exemplo, o número  $1101,11_{(2)}$ , que tem por equivalente decimal o número que resulta da soma

Sistema binário Base 2 Bit

$$\begin{aligned} 1 \times 2^3 + 1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0 + 1 \times 2^{-1} + 1 \times 2^{-2} &= \\ &= 1 \times 8 + 1 \times 4 + 1 \times 1 + 1 \times \frac{1}{2} + 1 \times \frac{1}{4} \\ &= 8 + 4 + 1 + 0, 5 + 0, 25 = 13, 75_{(10)}. \end{aligned}$$

Como podemos constatar, a dízima é, neste caso, finita. Escrevemos, então,

$$1101, 11_{(2)} = 13, 75_{(10)}$$

se quisermos duas casas na parte decimal, ou

$$1101, 11_{(2)} \simeq 13, 8_{(10)}$$

se apenas quisermos uma casa decimal, ou ainda

$$1101, 11_{(2)} \simeq 14_{(10)}$$

se não quisermos nenhuma.

Para o sistema de numeração binário é útil o conhecimento das potências de 2 mais importantes, porque nos ajuda a manejar com mais facilidade os pesos  $b^i$  necessários às conversões entre bases.

Por exemplo, ajuda saber que o 1 mais significativo (com maior peso, mais à esquerda) no número  $110100011_{(2)}$  tem peso  $2^8=256$ .

Na Tabela 1.1 representam-se algumas potências  $2^n$ , para valores inteiros de n entre -10 e +10.

| 2 <sup>n</sup>                            | n                               | 2 <sup>-n</sup>                                                                   |

|-------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------|

| 1<br>2<br>4<br>8<br>16<br>32<br>64<br>128 | 0<br>1<br>2<br>3<br>4<br>5<br>6 | 1, 0<br>0, 5<br>0, 25<br>0, 125<br>0, 0625<br>0, 03125<br>0, 015625<br>0, 0078125 |

| 256<br>512                                | 8<br>9                          | 0,00390625<br>0,001953125                                                         |

| 1k = 1024                                 | 10                              | 0,0009765625                                                                      |

Tabela 1.1: Potências  $2^n$ , para n inteiro entre -10 e +10

Em particular, chama-se a atenção para a designação 1k dada à potência  $2^{10} = 1024_{(10)}$ , que é a potência de 2 que mais se aproxima de  $1000_{(10)}$  (por essa razão, o factor k toma a designação habitual de "quilo" no sistema binário).

Para 10 < n < 20 usam-se exclusivamente estas designações. Por exemplo,

$$2^{16} = 2^6 \times 2^{10} = 64 \times 1024_{(10)} = 65536_{(10)}$$

valor este que habitualmente se designa por 64 k.

Para n=20 usa-se a potência

$$2^{20} = 2^{10} \times 2^{10} = 1024 \times 1024 = 1048576$$

.

Também neste caso  $2^{20}=1\,\mathrm{M}=1\,\mathrm{k}\times1\,\mathrm{k}$  é a potência de 2 que mais se aproxima de  $10^6_{(10)}$ , pelo que o factor M toma a designação habitual de "mega".

Finalmente, para n = 30 usa-se a potência

$$2^{30} = 1 \,\mathrm{M} \times 1 \,\mathrm{k} = 1 \,\mathrm{G}$$

.

Sendo 1 G a potência de 2 que mais se aproxima de  $10^9_{(10)}$ , o factor G toma a designação habitual de "giga".

Assim, temos, por exemplo,

$$2^{23} = 2^3 \times 2^{20} = 8 \,\mathrm{M}$$

е

$$2^{39} = 2^9 \times 2^{30} = 512 \,\mathrm{G}$$

.

#### 1.1.2 Representação na base 16

No sistema hexadecimal, com base b=16, usamos 16 dígitos. É claro, teremos que encontrar 16 representações (símbolos) diferentes para cada um deles.

Sistema hexadecimal Base 16

No sistema decimal usamos os dígitos 0 a 9, que podemos continuar a utilizar no sistema hexadecimal. Mas agora precisamos de "inventar" dígitos. A forma habitual de o fazer consiste em recorrer às primeiras 6 letras do alfabeto para representar os dígitos hexadecimais que, no sistema decimal, correspondem aos números (sequências de dois dígitos) 10 a 15. Então, no sistema hexadecimal usamos, para além dos símbolos 0 a 9, também as letras "a" a "f", ou, o que é o mesmo, "A" a "F".

E como estabelecer os equivalentes decimais destas letras? É simples: fazemos

$$\begin{split} A_{(16)} &= a_{(16)} = 10_{(10)} \,, \\ B_{(16)} &= b_{(16)} = 11_{(10)} \,, \\ & \cdots \\ F_{(16)} &= f_{(16)} = 15_{(10)} \,. \end{split}$$

Naturalmente os dígitos decimais mantêm-se no sistema hexadecimal:  $0_{(16)} = 0_{(10)}, 1_{(16)} = 1_{(10)},$  etc.

Por exemplo, um número hexadecimal legítimo é F30, $\mathrm{DA}_{(16)}$ , que terá por equivalente decimal o número que resulta da soma

$$\begin{split} 15\times16^2 + 3\times16^1 + 0\times16^0 + 13\times16^{-1} + 10\times16^{-2} &= \\ &= 15\times256 + 3\times16 + 13\times\frac{1}{16} + 10\times\frac{1}{256} \\ &= 3840 + 48 + 0,8125 + 0,0390625 \\ &= 3888,8515625_{(10)} \,. \end{split}$$

Mais uma vez, estamos na presença de um número com uma dízima finita. Escrevemos, então, por exemplo

$$F30, DA_{(16)} \simeq 3888, 9_{(10)}$$

se apenas quisermos uma precisão de uma casa decimal (neste caso arredondámos a dízima).

#### 1.2 Conversão entre Bases

#### 1.2.1 Conversão entre a base 10 e as bases 2 e 16

Uma vez que já sabemos obter o equivalente decimal de um número escrito no sistema binário ou no sistema hexadecimal (no fundo, já sabemos converter da base 2 ou 16 para a base 10), precisamos agora de aprender a converter da base 10 para a base 2 ou para a base 16, e ainda entre as bases 2 e 16.

No caso geral, o problema da conversão entre sistemas de numeração consiste no seguinte: dado um número N representado num sistema de base  $b_1$ , ou

seja, dado  $N_{(b_1)}$ , pretende-se representar esse número num sistema de base  $b_2$ , obtendo-se  $N_{(b_2)}$ .

No caso geral, quando  $b_1 \neq 10$  e  $b_2 \neq 10$ , a mudança pode efectuar-se directamente, utilizando operações aritméticas na base  $b_1$  ou na base  $b_2$ , existindo para tanto algoritmos apropriados para os dois casos.

Contudo, a mudança vem geralmente facilitada se for efectuada através do sistema de numeração de base 10, utilizando-se exclusivamente operações aritméticas nessa base. Assim, por exemplo, para converter um número, dado no sistema de base  $b_1=3$ , para o seu equivalente no sistema com base  $b_2=7$ , converte-se primeiro o número para o seu equivalente na base 10 e, em seguida, opera-se a conversão para a base  $b_2=7$ .

Este processo não introduz erros no tocante à conversão da parte inteira. Contudo, a conversão da parte fraccionária nem sempre dá um resultado finito e, nesses casos, há que arredondá-lo ou truncá-lo. Então, a utilização da base 10 como passo intermédio pode, se não pusermos os cuidados devidos, provocar uma acumulação de erros que devemos evitar.

Quando  $b_1 = 10$  e  $b_2 \neq 10$ , a conversão pode ser feita com as operações aritméticas na base  $b_2$ , o que torna esse método por vezes incómodo. Por isso, usa-se frequentemente um método diferente que utiliza a aritmética da base  $b_1$ , isto é, a aritmética decimal. Nesse método opera-se em duas fases, uma que trata a parte inteira, e outra que trata a parte decimal do número.

Método das divisões sucessivas

A conversão da parte inteira é feita pelo **método das divisões sucessivas**, que consiste em reter os restos das sucessivas divisões por  $b_2$  do número decimal dado e dos quocientes entretanto obtidos, até obter um quociente nulo.

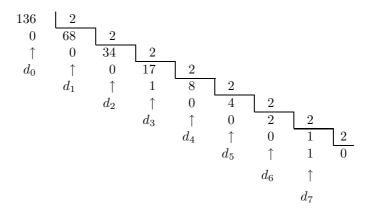

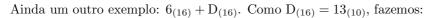

Como exemplo, admitamos que queríamos converter  $136_{(10)}$  para a base 2. Fazemos as seguintes divisões:

Obtemos, assim,

$$136_{(10)} <> 10001000_{(2)}$$

.

Método das multiplicações sucessivas Para a conversão da parte decimal utiliza-se o **método das multiplicações sucessivas**, que consiste em reter as partes inteiras das multiplicações por  $b_2$  da parte decimal dada e das sucessivas partes decimais entretanto obtidas, até que seja atingida a precisão pretendida para a parte fraccionária do número convertido (mais à frente estudaremos a questão da precisão mais em pormenor).

Por exemplo, para converter  $0,375_{(10)}$  para a base 2 fazemos

$$\begin{array}{lll} 0,375\times 2=0,750 & \rightarrow & d_{-1}=0 \\ 0,750\times 2=1,500 & \rightarrow & d_{-2}=1 \\ 0,500\times 2=1,000 & \rightarrow & d_{-3}=1 \,. \end{array}$$

Ou seja,  $0,375_{(10)} <> 0,011_{(2)}$  (neste caso particular obteve-se uma parte fraccionária finita).

A conversão de um número na base  $b_1 = 10$  para a base  $b_2 = 16$  pode ser feita usando os mesmos algoritmos. Basta, para isso, obter os restos das divisões por 16 e as partes inteiras das multiplicações por 16. Contudo, existe um processo mais expedito que consiste em converter o número dado para a base 2, e em seguida convertê-lo para a base 16 utilizando o método que iremos estudar já a seguir.

#### 1.2.2 Conversão da base 2 para a base 16

Este processo de conversão vem simplificado (não necessitamos de passar pela base 10) porque a base  $b_2 = 16$  é uma potência da base  $b_1 = 2$ .

Para percebermos o que está em jogo, vamos estabelecer um paralelo entre cada dígito hexadecimal e o seu equivalente binário.

Vamos então escrever, na Tabela 1.2, essas equivalências (já agora, incluímos também os equivalentes decimais).

Como podemos constatar, cada dígito hexadecimal é formado sempre por sequências de 4 dígitos binários.

Então, no processo de conversão para a base 16 basta-nos formar grupos de 4 bits a partir da vírgula do número binário, para a esquerda e para a direita, e escrever um dígito hexadecimal por cada grupo. Nos casos em que, ao fazermos os agrupamentos, restam grupos com menos do que 4 bits (nas posições mais significativas e menos significativas), preenchem-se esses agrupamentos com zeros não significativos até ficarem com 4 bits.

Por exemplo, para converter  $11110,101_{(2)}$  para a base 16 fazemos os agrupamentos

```

0001 1110 , 1010

```

e as correspondências

de onde resulta que 11110,  $101_{(2)} = 1E$ ,  $A_{(16)}$ .

#### 1.2.3 Conversão da base 16 para a base 2

Este processo de conversão é o oposto do anterior: o número na base 16 vê cada um dos seus dígitos decomposto em 4 bits. Por exemplo, se quisermos converter para binário o número 4A9,  $E_{(16)}$  fazemos

| Tabela 1.2: Equivalências entre os dígitos hexadecimais e as sequência de o | lígitos |

|-----------------------------------------------------------------------------|---------|

| (números) binários e decimais                                               |         |

|                                                                             |         |

| Dígito<br>hexadecimal | Número<br>binário | Número<br>decimal |

|-----------------------|-------------------|-------------------|

| 0                     | 0000              | 0                 |

| 1                     | 0001              | 1                 |

| 2                     | 0010              | 2                 |

| 3                     | 0011              | 3                 |

| 4                     | 0100              | 4                 |

| 5                     | 0101              | 5                 |

| 6                     | 0110              | 6                 |

| 7                     | 0111              | 7                 |

| 8                     | 1000              | 8                 |

| 9                     | 1001              | 9                 |

| A                     | 1010              | 10                |

| В                     | 1011              | 11                |

| C                     | 1100              | 12                |

| D                     | 1101              | 13                |

| E                     | 1110              | 14                |

| F                     | 1111              | 15                |

de onde resulta que 4A9,  $E_{(16)}=100101010101$ , 111 (notar que se eliminaram os zeros não significativos nas posições mais e menos significativas).

É claro que este método é válido para qualquer conversão em que  $b_1$  e  $b_2$  se relacionam por potências de 2. Por exemplo, para converter um número da base 4 para a base 2 decompomos cada dígito do número na base 4 em dois dígitos binários (porque  $4=2^2$ ). Identicamente, para converter um número da base 3 para a base 9 agrupamos cada conjunto de 2 dígitos do número na base 3 para formar um dígito na base 9 (porque  $9=3^2$ ).

#### 1.2.4 Truncagens e arredondamentos

Vamos definir em seguida os critérios de arredondamento da parte fraccionária de um número, quando há lugar a tal. Quando não se justificar fazer um arredondamento, truncamos a parte fraccionária.

Em primeiro lugar, nem sempre se torna necessário arredondar a parte fraccionária de um número. Por exemplo, se o número a representar for abstracto, sem conteúdo físico, pode não fazer sentido proceder ao seu arredondamento. Assim, uma representação para o número  $\pi$  com a parte fraccionária reduzida a p dígitos só faz sentido porque não queremos com ela encher várias folhas

de papel (nesses casos, o número p de casas fraccionárias é-nos imposto pela precisão dos cálculos em que  $\pi$  estiver envolvido).

Pelo contrário, se quisermos representar o resultado de uma medição física, por exemplo da corrente eléctrica que, num dado momento, circula por um circuito electrónico de baixa potência, a precisão da medição vem naturalmente limitada pela precisão do miliamperímetro que a mediu. Não faz sentido, nesse caso, "inventar" uma precisão que não existe, inserindo dígitos na parte fraccionária que não possuem conteúdo físico.

Consideremos um exemplo: uma determinada medição de corrente produziu um valor de 13,75 mA, ou seja, um resultado com uma precisão de 1 unidade em 100 (1/100). A conversão deste número decimal no seu equivalente numa base  $b_2$ , qualquer que ela seja, não deve "inventar" precisão. Quer isso dizer que não devemos obter um resultado que, após conversão, venha com uma precisão superior a 1/100.

Por exemplo, se convertermos o número  $13,75_{(10)}$  para binário obtemos o número  $1101,11000\cdots$  Mas qual será a representação binária correcta para 13,75 mA?

Se retivermos um dígito binário na parte fraccionária, obtemos um resultado com uma precisão de 1 unidade em  $2^1=2$ , isto é, de 0,5 (inferior à precisão do número original, que é igual a 1/100).

Se retivermos dois dígitos binários na parte fraccionária, obtemos um resultado com uma precisão de 1 unidade em  $2^2 = 4$ , isto é, de 0,25 (ainda inferior à precisão do número original). E por aí fora.

Se agora retivermos 6 dígitos binários na parte fraccionária, obtemos um resultado com uma precisão de 1 unidade em  $2^6=64$ , isto é, ainda inferior à precisão do número dado.

Mas se retivermos 7 dígitos binários na parte fraccionária, obtemos um resultado com uma precisão de 1 unidade em  $2^7 = 128$ , e 1/128 é uma precisão superior à que nos é dada. Ou seja, "inventámos" precisão onde ela não existia.

Segue-se que, com este exemplo, devemos apresentar 6 dígitos binários na parte fraccionária, e  $13,75_{(10)}$  mA  $<>1101,110000_{(2)}$  mA.

Neste exemplo não tivemos que arredondar o resultado (limitámo-nos a truncá-lo), mas há casos em que temos que o fazer. Isso é particularmente evidente quando o processo de conversão gera uma parte fraccionária infinita ou infinita periódica; mas também nos casos em que se obtêm partes fraccionárias finitas pode-se justificar arredondá-las se, por motivos de precisão, as quisermos com menos dígitos.

Considere-se então a representação

$$N_{(b)} \iff d_{q-1} d_{q-2} \cdots d_1 d_0, d_{-1} \cdots d_{-i} d_{-i-1} \cdots,$$

do número N na base b.

O problema do arredondamento da parte fraccionária de um número consiste em determinar o que fazer ao dígito  $d_{-i}$  em função do dígito  $d_{-i-1}$ . E essa decisão vai ser diferente consoante as bases forem pares ou ímpares.

Nas bases pares divide-se b por 2, formando-se desta forma dois conjuntos de dígitos que designaremos por parte baixa e por parte alta. Por exemplo, na

Naturalmente, nos casos em que  $d_{-i}$  não vem alterado há truncagem em vez de arredondamento.

base 10 obtemos uma parte baixa com o conjunto de dígitos  $\{0, 1, 2, 3, 4\}$  e uma parte alta com o conjunto  $\{5, 6, 7, 8, 9\}$ . O critério de arredondamento é, então, o seguinte: se o dígito  $d_{-i-1}$  estiver contido na parte baixa,  $d_{-i}$  não vem alterado; no caso contrário, soma-se uma unidade a  $d_{-i}$ .

Por exemplo, o número  $0.997_{(10)}$  vem arredondado para  $1.00_{(10)}$  se quisermos reter duas casas decimais (notar como a soma de uma unidade ao 9 na casa das centésimas se propagou até às unidades).

Da mesma forma, o número 111,  $11110_{(2)}$  vem arredondado para  $1000,000_{(2)}$  se quisermos reter três casas na parte fraccionária (a soma de uma unidade ao 1 com peso  $2^{-3}$  propaga-se para a parte inteira).

Nas bases ímpares, ao dividir-se b por dois obtêm-se duas partes com igual número de dígitos, tal como acontece com as bases pares, mas obtém-se ainda um dígito que "fica de fora". Por exemplo, para uma base b=5 obtém-se uma parte baixa com o conjunto de dígitos  $\{0,1\}$  e uma parte alta com o conjunto  $\{3,4\}$ , "sobejando" o dígito  $\{2\}$ .

O que se faz nestes casos é não alterar o dígito  $d_{-i}$  se o dígito  $d_{-i-1}$  estiver contido na parte baixa, e somar uma unidade a  $d_{-i}$  nos outros dois casos, Por exemplo, os números  $302,024_{(5)}$  e  $302,022_{(5)}$  vêm arredondados para  $302,03_{(5)}$  se quisermos reter duas casas na parte fraccionária, enquanto que o número  $302,021_{(5)}$  vem truncado para  $302,02_{(5)}$  nas mesmas condições.

#### 1.3 Aritmética Binária

#### 1.3.1 Adições na base 2 e noutras bases

Consideremos o seguinte exemplo de adição:  $435_{(10)} + 389_{(10)} = 824_{(10)}$ . Pretendemos, com o exemplo, deduzir o algoritmo da adição nesta base.

Esquematicamente temos:

Algoritmo da adição

Transporte na adição

Começa-se pela coluna 1 (da direita). Se o resultado da adição nessa coluna não exceder o valor b=10, o resultado vem colocado nessa coluna, sem alteração. Se o resultado da adição nessa coluna for igual a, ou exceder, o valor b=10, o que se coloca nessa coluna é a diferença entre o valor produzido e b, gerando-se, então, um **transporte**, C, para a coluna seguinte (a designação C vem da palavra em inglês "Carry").

Passa-se em seguida à coluna 2, onde se repete a operação anterior, somando ainda o transporte proveniente da coluna 1, se existir. E o mesmo acontece com as restantes colunas.

No nosso exemplo a adição na primeira coluna produziu um transporte,

13

Tabela 1.3: Tabela da adição no sistema binário

| Adição binária |   |   |    |  |  |  |  |  |  |  |

|----------------|---|---|----|--|--|--|--|--|--|--|

| +              | - | 0 | 1  |  |  |  |  |  |  |  |

| -              | ) | 0 | 1  |  |  |  |  |  |  |  |

| 1              |   | 1 | 10 |  |  |  |  |  |  |  |

$$\begin{array}{ccc}

1 & \leftarrow \text{coluna} \\

5 & \\

+ & 9 & \\

\hline

1 & 4 & \\

C=1 & & \\

\end{array}$$

e na coluna 2 tivemos de adicionar esse transporte aos operandos na coluna, gerando um novo transporte,

$$\begin{array}{ccc}

2 & \leftarrow \text{coluna} \\

1 & & \\

3 & \\

+ & 8 & \\

\hline

1 & 2 & \\

C=1 & &

\end{array}$$

O algoritmo da adição binária é em tudo semelhante ao da adição no sistema decimal (e, de facto, ao da adição em qualquer sistema de numeração posicional), excepto que se utiliza b=2 em vez de b=10.

Começa-se, então, pela coluna da direita, vindo o resultado da adição colocado ainda nessa coluna. Desde que não exceda o valor b=2, como por exemplo em

$$\begin{array}{ccc}

& 1 \\

& + & 0 \\

\hline

& 1_{(2)}

\end{array}$$

o resultado vem colocado nessa coluna, sem alteração (para efectuar a adição binária, consultar a Tabela 1.3, que contém a operação de adição binária de dois operandos com um bit cada um).

Se o resultado da adição for igual a, ou exceder, o valor b=2, haverá que colocar nessa coluna o valor da diferença entre o valor produzido e b, gerando-se, então, um transporte para a coluna seguinte. Por exemplo,  $1_{(2)}+1_{(2)}$  dá um valor  $10_{(2)}$ , ou  $2_{(10)}$ , que é igual a b=2. Então, o que se coloca nessa coluna é a diferença entre o valor  $2_{(10)}$  que se produziu e o valor b=2, obtendo-se b=20 e um transporte b=20 e um transpo

|                 |   |              |              |              |              | Α            | diçã         | o he         | xade         | cima         | ı            |              |              |              |    |    |

|-----------------|---|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|----|----|

| +               | 0 | 1            | 2            | 3            | 4            | 5            | 6            | 7            | 8            | 9            | A            | В            | С            | D            | Е  | F  |

| 0               | 0 | 1            | 2            | 3            | 4            | 5            | 6            | 7            | 8            | 9            | A            | В            | С            | D            | E  | F  |

| 1               | 1 | 2            | 3            | 4            | 5            | 6            | 7            | 8            | 9            | A            | В            | $\mathbf{C}$ | D            | $\mathbf{E}$ | F  | 10 |

| 2               | 2 | 3            | 4            | 5            | 6            | 7            | 8            | 9            | A            | В            | $\mathbf{C}$ | D            | $\mathbf{E}$ | F            | 10 | 11 |

| 3               | 3 | 4            | 5            | 6            | 7            | 8            | 9            | A            | В            | $\mathbf{C}$ | D            | $\mathbf{E}$ | F            | 10           | 11 | 12 |

| 4               | 4 | 5            | 6            | 7            | 8            | 9            | A            | В            | $\mathbf{C}$ | D            | $\mathbf{E}$ | F            | 10           | 11           | 12 | 13 |

| 5               | 5 | 6            | 7            | 8            | 9            | A            | В            | $\mathbf{C}$ | D            | $\mathbf{E}$ | $\mathbf{E}$ | 10           | 11           | 12           | 13 | 14 |

| 6               | 6 | 7            | 8            | 9            | A            | В            | $^{\rm C}$   | D            | $\mathbf{E}$ | F            | 10           | 11           | 12           | 13           | 14 | 15 |

| 7               | 7 | 8            | 9            | A            | В            | $\mathbf{C}$ | D            | $\mathbf{E}$ | F            | 10           | 11           | 12           | 13           | 14           | 15 | 16 |

| 8               | 8 | 9            | A            | В            | $\mathbf{C}$ | D            | $\mathbf{E}$ | F            | 10           | 11           | 12           | 13           | 14           | 15           | 16 | 17 |

| 9               | 9 | A            | В            | $^{\rm C}$   | D            | $\mathbf{E}$ | F            | 10           | 11           | 12           | 13           | 14           | 15           | 16           | 17 | 18 |

| A               | A | В            | $\mathbf{C}$ | D            | $\mathbf{E}$ | F            | 10           | 11           | 12           | 13           | 14           | 15           | 16           | 17           | 18 | 19 |

| В               | В | $^{\rm C}$   | D            | $\mathbf{E}$ | F            | 10           | 11           | 12           | 13           | 14           | 15           | 16           | 17           | 18           | 19 | 1A |

| $^{\mathrm{C}}$ | С | D            | $\mathbf{E}$ | F            | 10           | 11           | 12           | 13           | 14           | 15           | 16           | 17           | 18           | 19           | 1A | 1B |

| D               | D | $\mathbf{E}$ | F            | 10           | 11           | 12           | 13           | 14           | 15           | 16           | 17           | 18           | 19           | 1A           | 1B | 1C |

| $\mathbf{E}$    | E | F            | 10           | 11           | 12           | 13           | 14           | 15           | 16           | 17           | 18           | 19           | 1A           | 1B           | 1C | 1D |

| F               | F | 10           | 11           | 12           | 13           | 14           | 15           | 16           | 17           | 18           | 19           | 1A           | 1B           | 1C           | 1D | 1E |

|                 |   |              |              |              |              |              |              |              |              |              |              |              |              |              |    |    |

Tabela 1.4: Tabela da adição no sistema hexadecimal

O valor do transporte que for gerado é adicionado aos valores da coluna imediatamente à esquerda, e o algoritmo prossegue de forma idêntica para todas as colunas.

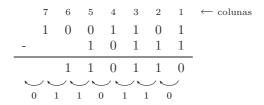

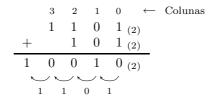

Por exemplo, para efectuar a adição  $1111_{(2)} + 101_{(2)}$  fazemos

De notar que

$$\begin{array}{cccc} 1111_{(2)} & <> & 15_{(10)} \\ 101_{(2)} & <> & 5_{(10)} \\ 10100_{(2)} & <> & 20_{(10)} \, . \end{array}$$

De notar ainda que na coluna 3 se procedeu à adição de três unidades, gerando uma soma igual a 1 e um transporte C=1.

No sistema hexadecimal utilizamos ainda o mesmo algoritmo da adição. Naturalmente, teremos agora que saber adicionar dois dígitos hexadecimais, para o que utilizamos a Tabela 1.4.

Vamos ver, com alguns exemplos, como se constroi esta tabela.

Por exemplo, a adição  $4_{(16)}+9_{(16)}$  é a mesma que  $4_{(10)}+9_{(10)}$ , o que dá  $13_{(10)}$ . Mas  $13_{(10)}$  corresponde a um único dígito na base 16, o dígito  $D_{(16)}$ , que é menor do que a base b=16. Logo, o resultado da soma  $4_{(16)}+9_{(16)}$  dá  $D_{(16)}$  e não gera transporte.

Notemos como fazemos o raciocínio na base 10, porque estamos habituados a raciocinar nesta base (mas podíamos raciocinar numa base qualquer).

$$6_{(16)} + D_{(16)} = 6_{(10)} + 13_{(10)} = 19_{(10)}$$

.

Como  $19_{(10)} > 16_{(10)}$ , devemos reter o que resultar da subtracção  $19_{(10)} - 16_{(10)} = 3_{(10)} <> 3_{(16)}$  e gerar um transporte. Logo,  $6_{(16)} + D_{(16)} = 13_{(16)}$ .

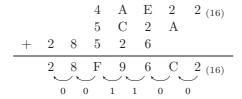

Passemos agora à adição de dois números na base 16, por exemplo  $4A57_{(16)} + D293_{(16)}$ . Faz-se:

#### 1.3.2 Subtracções na base 2 e noutras bases

O algoritmo da subtracção pode resumir-se ao seguinte: se numa coluna i, qualquer, o **aditivo** for maior do que o **subtractivo**, o resultado da subtracção vem na coluna i, sem alteração.

No caso contrário, soma-se a base ao aditivo e coloca-se na coluna i o resultado da diferença entre este valor e o subtractivo, gerando-se um **transporte** para a coluna i+1.

Assim, por exemplo,

fazendo-se a diferença (b+3)-8=(10+3)-8=5 na coluna mais à direita e gerando-se um transporte igual a 1 para a coluna imediatamente à esquerda.

De idêntica forma, no sistema binário faz-se, por exemplo,

ou seja, faz-se a diferença (b+0)-1=(2+0)-1=1 e gera-se um transporte.

Por exemplo, para efectuar a subtracção  $1001101_{(2)}-10111_{(2)}$  fazemos:

Algoritmo da subtracção Aditivo e subtractivo

Transporte na subtracção

Neste exemplo não é gerado transporte da coluna 1 para a coluna 2. Porém, na coluna 2 é gerado um transporte ("1 para 2 igual a 1, com transporte igual a 1") para a coluna 3. Esse transporte é adicionado, na coluna 3, ao subtractivo ("1 + 1 = 2, isto é,  $0_{(2)}$  e transporte 1") que depois é subtraído do aditivo ("0 para 1 igual a 1, mantendo-se o transporte"). De forma idêntica se procederia com as colunas 4 a 7.

Na base 16 temos o mesmo algoritmo. Por exemplo, para efectuar 9F1B $_{(16)}-4A36_{(16)}$  faz-se:

De notar, na coluna 2, que se faz " $3_{(10)}$  para  $17_{(10)}$ , o que dá  $14_{(10)} <> E_{(16)}$ , gerando-se um transporte igual a 1". De notar ainda que, na coluna 3, se faz " $A_{(16)} = 10_{(10)}$  mais o transporte 1 dá  $11_{(10)}$ ;  $11_{(10)}$  para  $F_{(16)} <> 15_{(10)}$  dá  $4_{(10)} <> 4_{(16)}$ , gerando-se um transporte nulo".

É de notar que este algoritmo produz um resultado incorrecto quando o subtractivo é maior que o aditivo. Com efeito, a aplicação do algoritmo nestas situações produz um transporte que se vai propagar indefinidamente a partir de uma coluna i e sucessivamente para as colunas i+1, i+2, etc. como no seguinte exemplo

Este problema só vem resolvido quando estudarmos os números com sinal e, em particular, quando se apresentar a representação em complemento para 2, na Subsecção 1.4.2.

#### 1.3.3 Multiplicação na base 2 e noutras bases

O produto de dois números numa base arbitrária vai, mais uma vez, obedecer ao algoritmo da multiplicação. Por exemplo, na base b=10 temos

Tabela 1.5: Tabela da multiplicação no sistema binário

| Multiplicação binária |   |   |  |  |  |  |  |  |  |

|-----------------------|---|---|--|--|--|--|--|--|--|

| ×                     | 0 | 1 |  |  |  |  |  |  |  |

|                       | U |   |  |  |  |  |  |  |  |

| 0                     | 0 | 0 |  |  |  |  |  |  |  |

| 1                     | 0 | 1 |  |  |  |  |  |  |  |

|                       |   |   |  |  |  |  |  |  |  |

|   | 1<br>× | 5<br>2 | $\frac{7}{3}_{(10)}^{(10)}$ |

|---|--------|--------|-----------------------------|

|   | 4      | 7      | 1                           |

| 3 | 1      | 4      |                             |

| 3 | 6      | 1      | 1 (10)                      |

Notemos que agora podemos ter transportes maiores do que a unidade. Por exemplo,

Da mesma forma, na base b=2 podemos multiplicar dois números desde que conheçamos a tabela de multiplicação de dois dígitos nessa base (Tabela 1.5).

Por exemplo,

Notemos como é fácil a multiplicação nesta base. Como cada dígito do multiplicador só pode ser 0 ou 1, a multiplicação desse dígito pelo multiplicando só pode dar o próprio multiplicando ou uma linha com zeros.

Para a multiplicação na base b=16 precisamos de conhecer a respectiva tabela (Tabela 1.6).

Vejamos como deduzir uma posição desta tabela (sabendo-se deduzir uma, pode deduzir-se a tabela toda).

Por exemplo, consideremos o produto  $C_{(16)} \times B_{(16)} = 84_{(16)}$ . A melhor forma de obter este resultado é raciocinar em decimal, como fizemos para as adições e para

|   | Multiplicação hexadecimal |              |              |              |              |    |              |              |    |               |    |    |              |    |               |    |

|---|---------------------------|--------------|--------------|--------------|--------------|----|--------------|--------------|----|---------------|----|----|--------------|----|---------------|----|

|   | l .                       |              |              |              |              |    |              |              |    |               |    |    |              |    |               |    |

| × | 0                         | 1            | 2            | 3            | 4            | 5  | 6            | 7            | 8  | 9             | A  | В  | С            | D  | Е             | F  |

| 0 | 0                         | 0            | 0            | 0            | 0            | 0  | 0            | 0            | 0  | 0             | 0  | 0  | 0            | 0  | 0             | 0  |

| 1 | 0                         | 1            | 2            | 3            | 4            | 5  | 6            | 7            | 8  | 9             | A  | В  | $\mathbf{C}$ | D  | $\mathbf{E}$  | F  |

| 2 | 0                         | 2            | 4            | 6            | 8            | A  | $\mathbf{C}$ | $\mathbf{E}$ | 10 | 12            | 14 | 16 | 18           | 1A | 1C            | 1E |

| 3 | 0                         | 3            | 6            | 9            | $\mathbf{C}$ | F  | 12           | 15           | 18 | 1B            | 1E | 21 | 24           | 27 | 2A            | 2D |

| 4 | 0                         | 4            | 8            | $\mathbf{C}$ | 10           | 14 | 18           | 1C           | 20 | 24            | 28 | 2C | 30           | 34 | 38            | 3C |

| 5 | 0                         | 5            | A            | F            | 14           | 19 | 1E           | 23           | 28 | 2D            | 32 | 37 | 3C           | 41 | 46            | 4B |

| 6 | 0                         | 6            | $\mathbf{C}$ | 12           | 18           | 1E | 24           | 2A           | 30 | 36            | 3C | 42 | 48           | 4E | 54            | 5A |

| 7 | 0                         | 7            | $\mathbf{E}$ | 15           | 1C           | 23 | 2A           | 31           | 38 | 3F            | 46 | 4D | 54           | 5B | 62            | 69 |

| 8 | 0                         | 8            | 10           | 18           | 20           | 28 | 30           | 38           | 40 | 48            | 50 | 58 | 60           | 68 | 70            | 78 |

| 9 | 0                         | 9            | 12           | 1B           | 24           | 2D | 36           | 3F           | 48 | 51            | 5A | 63 | 6C           | 75 | $7\mathrm{E}$ | 87 |

| A | 0                         | A            | 14           | 1E           | 28           | 32 | 3C           | 46           | 50 | 5A            | 64 | 6E | 78           | 82 | 8C            | 96 |

| В | 0                         | В            | 16           | 21           | 2C           | 37 | 42           | 4D           | 58 | 63            | 6E | 79 | 84           | 8F | 9A            | A5 |

| C | 0                         | $\mathbf{C}$ | 18           | 24           | 30           | 3C | 48           | 54           | 60 | 6C            | 78 | 84 | 90           | 9C | A8            | B4 |

| D | 0                         | D            | 1A           | 27           | 34           | 41 | 4E           | 5B           | 68 | 75            | 82 | 8F | 9C           | A9 | В6            | C3 |

| E | 0                         | Е            | 1C           | 2A           | 38           | 46 | 54           | 62           | 70 | $7\mathrm{E}$ | 8C | 9A | A8           | В6 | 4             | D2 |

| F | 0                         | F            | 1E           | 2D           | 3C           | 4B | 5A           | 69           | 78 | 87            | 96 | A5 | B4           | C3 | D2            | E1 |

|   |                           |              |              |              |              |    |              |              |    |               |    |    |              |    |               |    |

Tabela 1.6: Tabela da multiplicação no sistema hexadecimal

as subtracções. Assim, C $_{(16)}<>12_{(10)}$ e B $_{(16)}<>11_{(10)}.$  Ora  $12_{(10)}\times11_{(10)}==132_{(10)}.$  Convertendo agora para hexadecimal obtemos

$$132_{(10)} = 128_{(10)} + 4_{(10)} = 8_{(10)} \times 16_{(10)} + 4_{(10)} <> 84_{(16)} \,.$$

Agora, multiplicar dois números hexadecimais é simples. Por exemplo,

Com efeito, reparemos como

ou como

#### 1.4 Números com Sinal

#### 1.4.1 Notação de sinal e módulo

A representação de números reais tem de ter em conta que os números podem ser positivos, negativos ou o número 0.

Num sistema digital, um número é sempre representado com um determinado número de bits, o comprimento do número, que corresponde ao número de bits dos registos onde o número é armazenado e ao número de bits dos circuitos que processam os números.

Suponhamos, para simplificar, e a titulo de exemplo, que o comprimento é de 4 bits.

Uma primeira ideia consiste em representar o número em **módulo e sinal**. O módulo já não nos oferece dificuldade, mas não é óbvio como podemos representar o sinal. A forma mais evidente é reservar um bit para o **sinal** e definir, por exemplo, que se esse bit for 0 o número é positivo e se for 1 é negativo.

Com quatro bits podemos, então, representar os números inteiros que se indicam na Tabela 1.7.

Esta forma de representar números inteiros é uma das formas possíveis. Tem, porém, alguns inconvenientes.

Em primeiro lugar, repare-se que existem duas representações para o número 0, o que pode originar problemas.

Em segundo lugar, quando é necessario fazer operações sobre os números assim representados, é necessario processar de forma diferente o módulo e o sinal, e é ainda necessário escolher a operação a realizar em termos da operação desejada e do sinal dos números.

Por exemplo, se pretendermos fazer a operação (+5)+(-3), o que é realmente necessário fazer é a subtracção 5-3, ficando o sinal positivo. Se o problema for realizar (-5)+(+3), então há que realizar também uma subtracção mas do módulo do número negativo menos o do positivo, sendo o resultado um número negativo.

Obviamente, tudo isto complica significativamente os circuitos lógicos que realizam a operação de soma (e também os que realizam a subtracção).

#### 1.4.2 Notação de complemento para 2

Seria interessante se pudéssemos representar os números de tal forma que fosse possível realizar as operações de soma e de subtracção sempre da mesma forma,

Representação de um número em módulo e sinal

Bit de sinal

| Representação | Número<br>representado |

|---------------|------------------------|

| 0000          | +0                     |

| 0001          | +1                     |

| 0010          | +2                     |

| 0011          | +3                     |

| 0100          | +4                     |

| 0101          | +5                     |

| 0110          | +6                     |

| 0111          | +7                     |

| 1000          | -0                     |

| 1001          | -1                     |

| 1010          | -2                     |

| 1011          | -3                     |

| 1100          | -4                     |

| 1101          | -5                     |

| 1110          | -6                     |

| 1111          | -7                     |

Tabela 1.7: Números com 4 bits representados em módulo e sinal

independentemente de os números serem positivos ou negativos. E isso é possível utilizando a representação em complemento para 2.

Complemento para 2 de um número

Comecemos por perceber o que é o **complemento para 2 de um número**. Ou, mais correctamente, o complemento para  $2^n$ . Designa-se por complemento para  $2^n$  de um número x com n bits o resultado da operação  $2^n-x$ . Obtemos, desta forma, o simétrico de x.

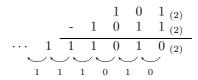

Por exemplo, o complemento para  $2^4$  de 0101 é

O número 1011 é, então, o complemento para  $2^4$  ou, mais simplesmente, o complemento para 2 de 0101.

Repare-se que, se o número x tem n bits, o seu complemento para 2 é representavel de igual modo com n bits.

É óbvio que o complemento para 2 de complemento para 2 de um número x é x, já que  $2^n-(2^n-x)=x$ . Assim, o complemento para 2 de 1011 é, como se pode verificar, 0101.

Uma forma mais expedita de obter o complemento para 2 de um número consiste, como se poderá verificar, em complementar (negar) todos os bits do número e somar-lhe 1. Novamente, tomando como exemplo o número 5 (0101),

pode obter-se o complemento para 2 de 5 negando-o (1010) e somando-lhe 1 (1011), o que vem dar o mesmo resultado que vimos atrás.

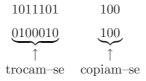

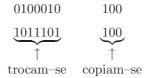

Ainda uma terceira forma para obter o complemento para 2 de um número utiliza o seguinte algoritmo: percorre-se a representação do número a complementar, desde o bit menos significativo até ao mais significativo. Por cada 0 que se encontra, reproduz-se esse 0. Quando se encontrar o primeiro 1, também se reproduz. A partir daí, trocam-se os "0"s com os "1"s.

Por exemplo, o complemento para 2 do número negativo 1011101100 é o número positivo 0100010100:

e o complemento para 2 do número positivo 0100010100 é o número negativo 1011101100:

Na notação de complemento para 2, os números são também representados de forma a que um dos bits (o **mais significativo**) represente o sinal. Tal como na representação em módulo e sinal, o bit a 0 indica que o número é positivo, e a 1 indica que o número é negativo. Portanto, com n bits para representar um número, "sobram" n-1 bits para além do sinal para representar, de alguma forma, o módulo do número (veremos já adiante que isso não é completamente verdade).

Na representação em complemento para 2 de um número positivo x, o número é representado pelo seu módulo. Por exemplo, o número  $+5_{(10)}$  é representado, em notação de complemento para 2 com 4 bits, como  $0101_{(C2)}$ , em que o índice referencia este modo de representação, ou notação (a notação de complemento para 2).

Na representação em complemento para 2 de um número negativo, o número x é representado pelo complemento para 2 de x.

Por exemplo o número  $-5_{(10)}$  é representado, em notação de complemento para 2, por  $1011_{(C2)}$ . Repare-se que a determinação do complemento para 2 de um número deixa já o bit de sinal do número simétrico com o valor correcto.

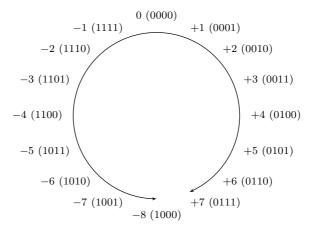

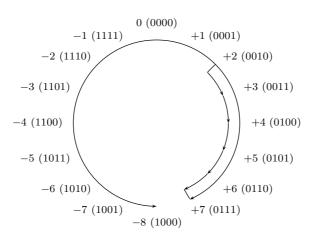

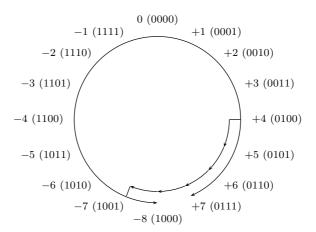

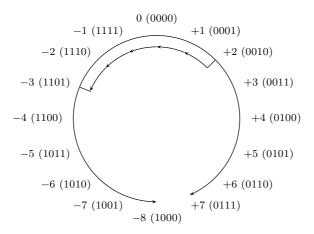

A representação dos 16 números possiveis em complemento para 2 com 4 bits vem ilustrada na Figura 1.1.

Como é natural, o número de números representáveis com n bits é de  $2^n$ . Como se pode ver da figura, o intervalo representado é  $[-2^{n-1}, +2^{n-1}-1]$ , no nosso caso [-8, +7]. A razão da assimetria entre o número de positivos e o de negativos

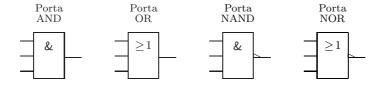

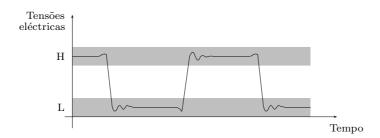

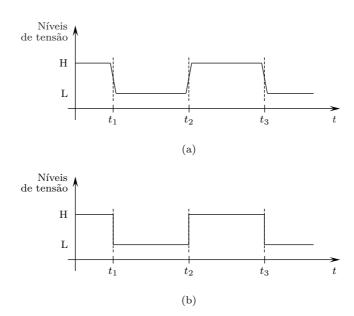

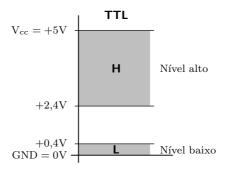

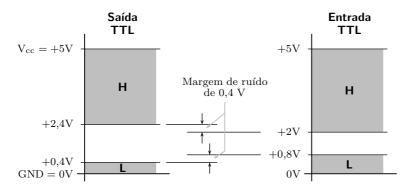

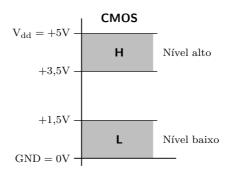

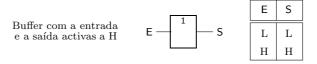

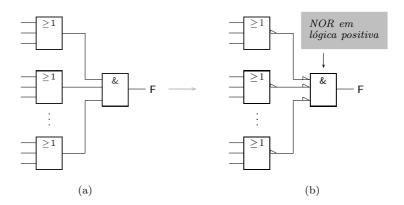

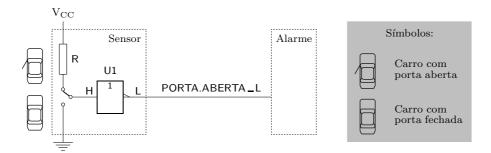

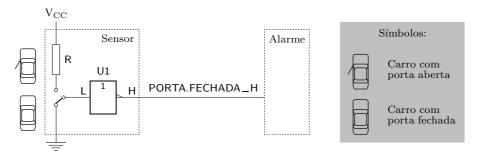

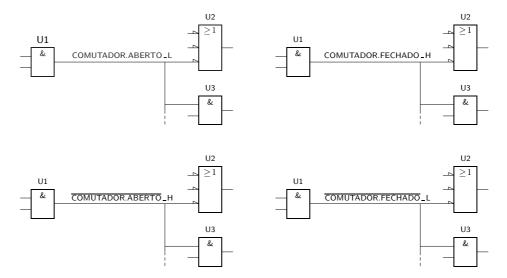

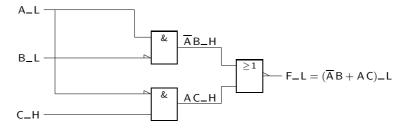

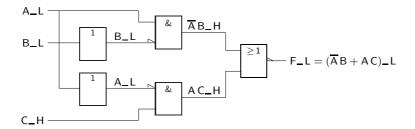

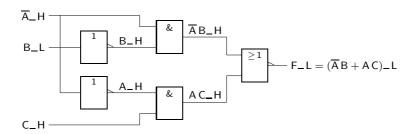

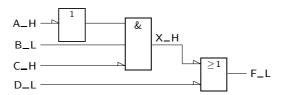

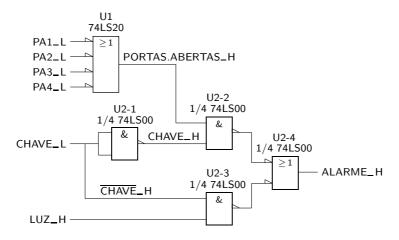

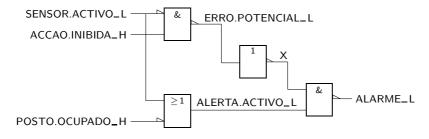

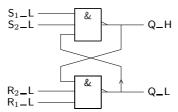

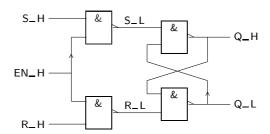

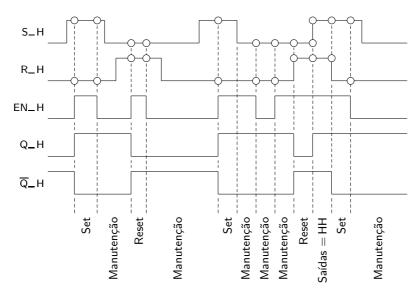

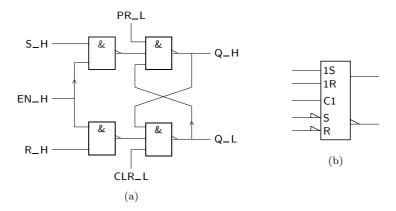

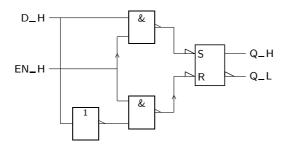

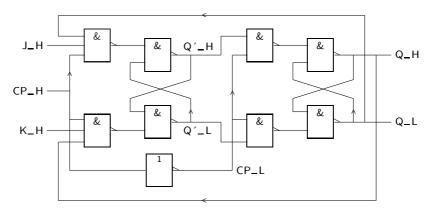

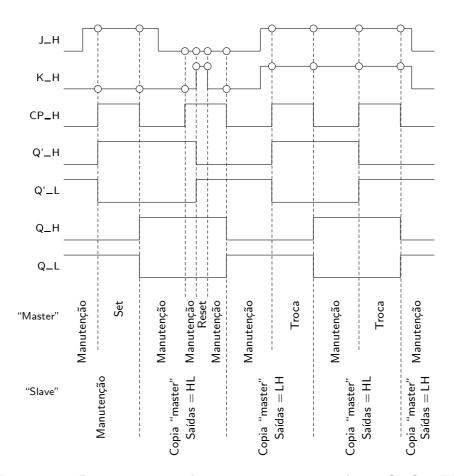

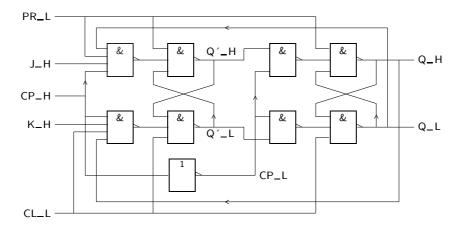

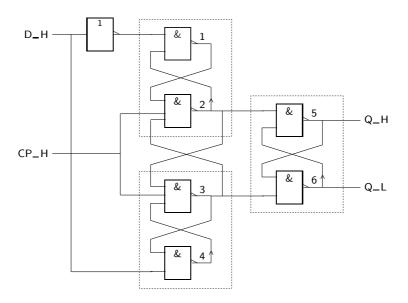

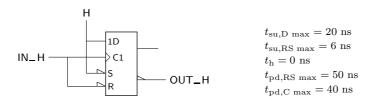

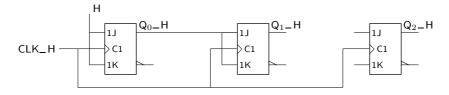

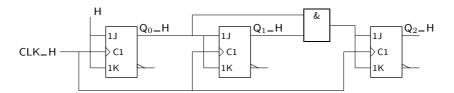

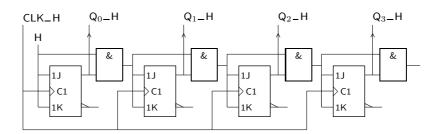

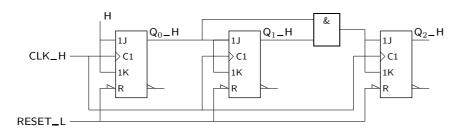

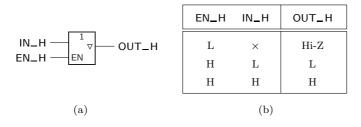

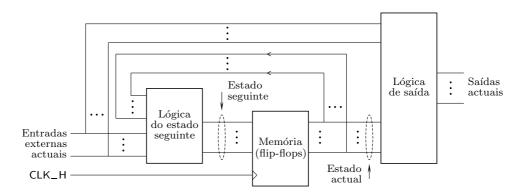

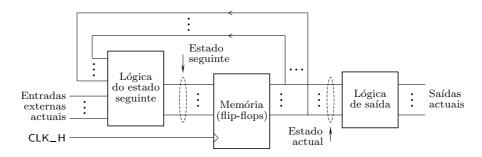

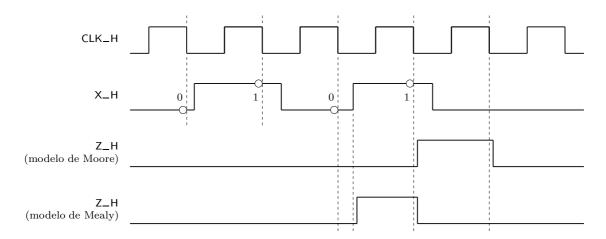

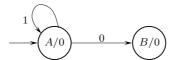

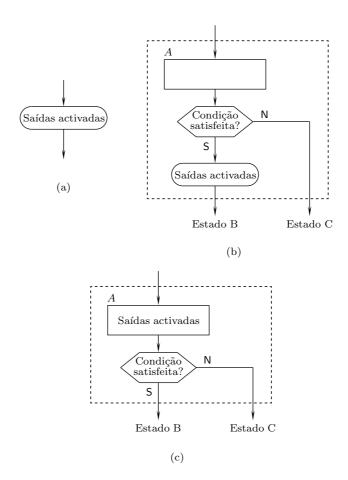

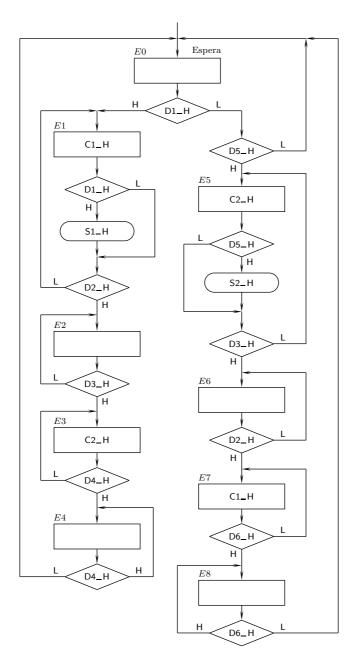

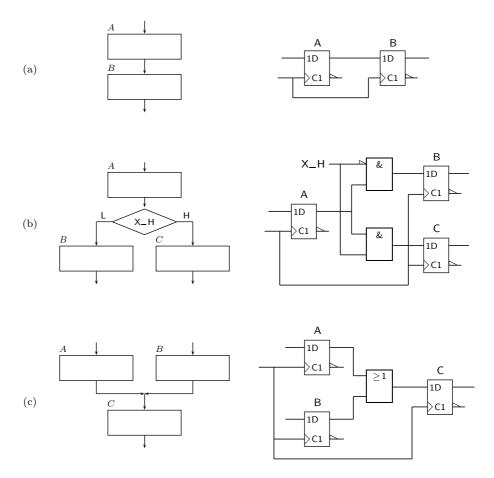

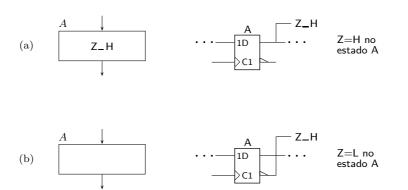

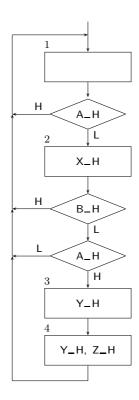

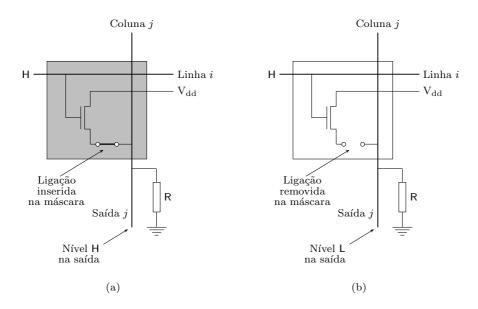

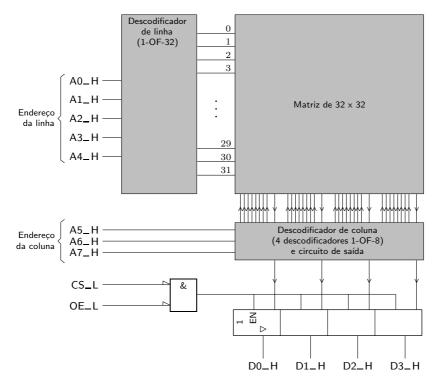

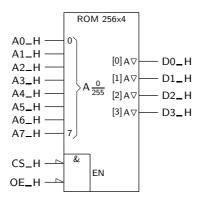

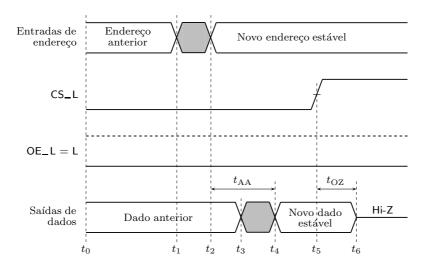

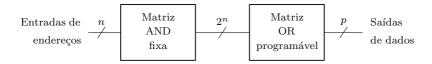

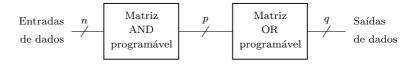

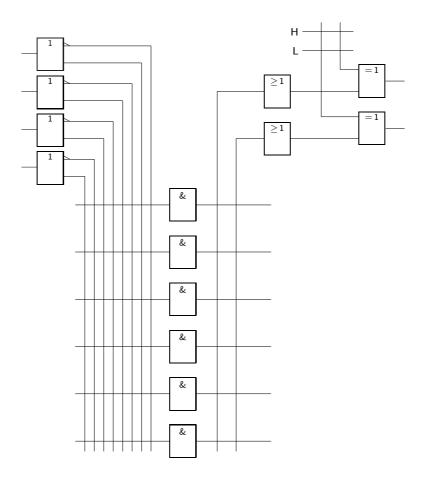

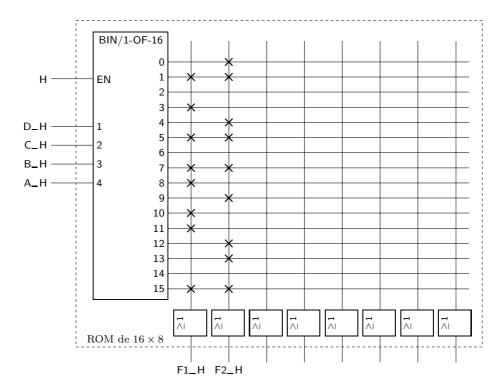

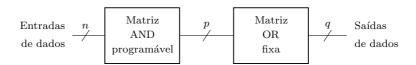

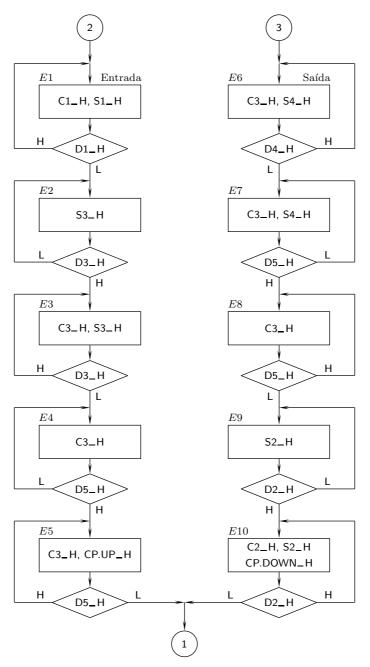

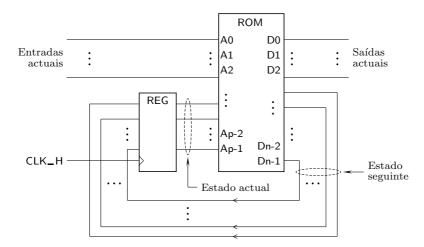

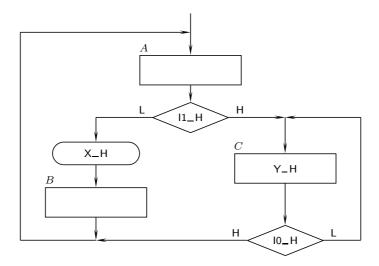

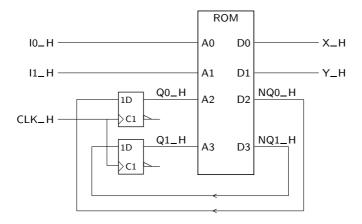

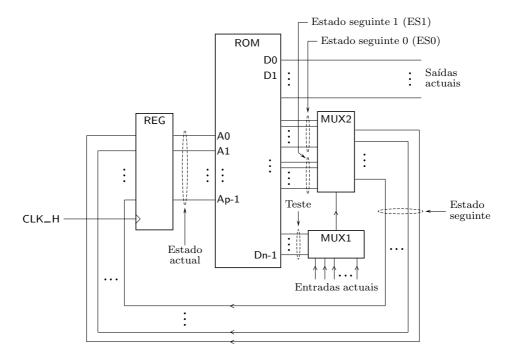

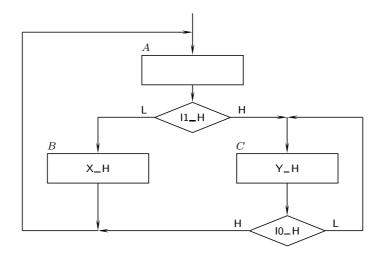

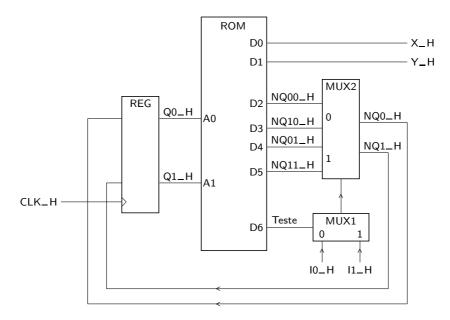

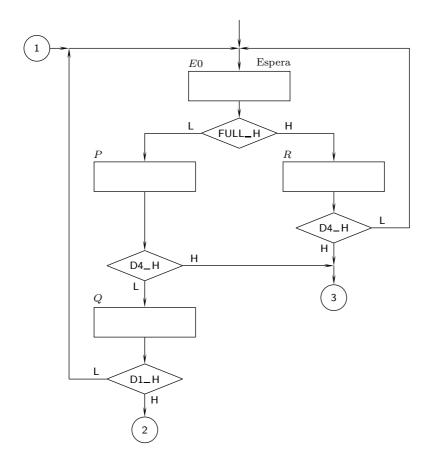

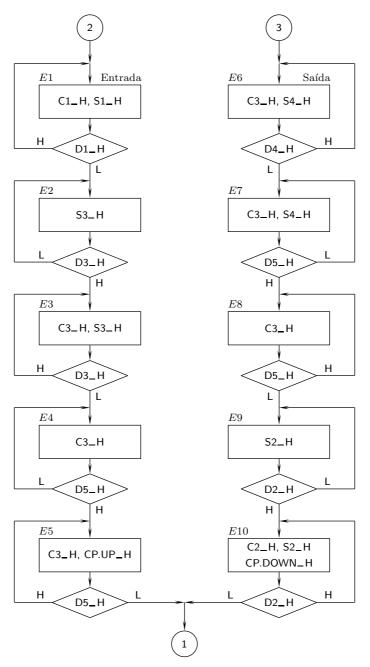

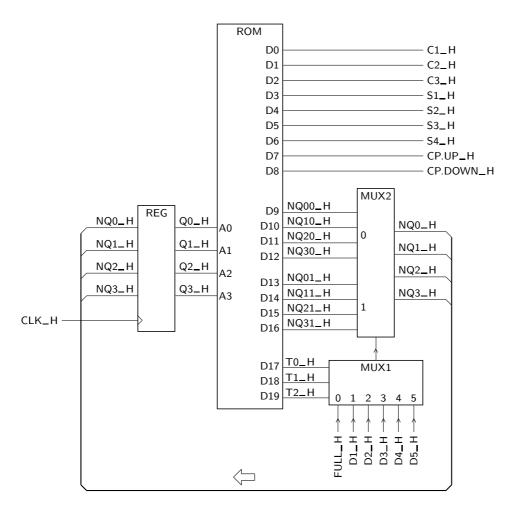

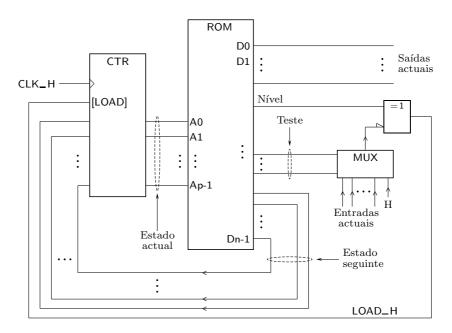

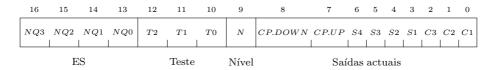

#### Bit mais significativo